Master's Thesis

Concurrency in Computational Networks

> S. Stuijk (446407)

Supervisors: dr. ir. A.A. Basten

prof. dr. ir. J.L. van Meerbergen

Date: October 2002

The department of Electrical Engineering of the Eindhoven University of Technology does not accept any responsibility regarding the contents of Master's Thesis

## Abstract

Future generations of embedded multi-media systems will have an increasing need for compute platforms that combine high compute power with low energy consumption. To meet with these requirements, multi-processor systems must be used. These systems are in nature concurrent, and this concurrency in the architecture should be exploited. This requires that the concurrency is used in the mapping trajectory from the system specification to the hardware architecture. The concurrency in an application should therefore be extracted, and made explicit, in the models that are used to specify a system. To support the extraction of concurrency from an application, the model must contain a concurrency model. This concurrency model should support formal reasoning about concurrency.

This thesis present a model of computation that can be used to explicitly specify the concurrency in an application. This model of computation, the computational-network model, is based on the Kahn process network model. The computational-network model is extended with a concurrency model. This concurrency model is comprised of five main measures supported by a set of detailed measures. These measures provide an insight in the concurrency properties of the specified system. The thesis presents also a first implementation of the presented model of computation and concurrency model.

The thesis presents a case study that shows that all of these five measures are meaningful and do not overlap. These experiments suggest further that the measures are sufficient for obtaining good results; no more measures are needed. The design case shows also that it is possible to perform a concurrency optimization that is architecture independent and to obtain results similar to an optimization performed by an experienced designer that optimizes the application for a given architecture.

# Acknowledgments

Over the last 9 months I had the opportunity to work in an excellent and inspiring environment, which eventually resulted in this thesis. I would like to thank Jef van Meerbergen, my graduation professor, for providing me that option. I would also like to thank Twan Basten, my supervisor, for giving me the opportunity to develop my own ideas. Though I always tried to come up with proven and watertight ideas, he always managed to find some bottlenecks to urge and motivate me to search for better solutions. From the early stages of this thesis until the final version, he was always able to help me structure my thesis and give useful feedback on how it could be improved. I also want to thank him for the many fruitful discussions we had about the subject. I also owe thanks to Johan Lukkien for taking place in my graduation commission and the useful suggestions that he gave me for finding related work.

I would also like to thank Jan Hoogerbrugge and Paul Stravers. They created the CAKE architecture and simulations environment which I used to prove that my models are working. I also want to thank Erwin de Kock for giving me a draft version of an article about a JPEG decoder case study that he performed. He also gave me the source code of all JPEG decoders presented in this article and he was the principal developer of the YAPI library. The article, the code and YAPI have proven to be very useful in this project.

Finally, I would like to thank Dirk and Etienne, my roommates, and all people of the ES group that are present every day in the groups coffee room for the many nice and interesting discussions we had during the coffee breaks.

# Contents

| 1 | Intr | roduction                 | 1  |

|---|------|---------------------------|----|

| 2 | Pro  | blem Definition           | 3  |

|   | 2.1  | Introduction              | 3  |

|   | 2.2  | System Architectures      | 4  |

|   | 2.3  | Application Specification | 5  |

|   | 2.4  | Multi-Processor Mapping   | 5  |

|   | 2.5  | Motivating Example        | 6  |

|   | 2.6  | Conclusion                | 8  |

| 3 | Mo   | del of Computation        | 9  |

|   | 3.1  | Introduction              | 9  |

|   | 3.2  | Computational Networks    | 9  |

|   | 3.3  | Executions                | 13 |

|   | 3.4  | Conclusion                | 19 |

| 4 | Cor  | ncurrency Model           | 21 |

|   | 4.1  | Introduction              | 21 |

|   | 4.2  | Assumptions               | 21 |

|   | 4.3  | Concurrency Measures      | 23 |

|   |      | 4.3.1 Computation Load    | 23 |

|   |      | 4.3.2 Execution Load      | 27 |

|   |      | 4.3.3 Restart Interval    | 30 |

|   |      | 4.3.4 Synchronization     | 32 |

|   |      | 4.3.5 Structure           | 34 |

|   | 4.4  | Examples                  | 38 |

|   | 4.5  | Related Work              | 44 |

|   | 4.6  | Conclusion                | 45 |

| 5 | Imp  | plementation              | 17 |

|   | 5.1  |                           | 47 |

|   | 5.2  |                           | 47 |

|   | 5.3  | <del>-</del>              | 48 |

|   |      | 1 0                       | 48 |

vi *CONTENTS*

|   |     | 5.3.2 Delay Function for Read and Write Events                                     | 50 |

|---|-----|------------------------------------------------------------------------------------|----|

|   |     | 5.3.3 Delay Function for Connections                                               | 52 |

|   | 5.4 | Concurrency Analysis and Simulation Tool                                           | 53 |

|   |     | 5.4.1 Introduction                                                                 | 53 |

|   |     | 5.4.2 Simulator                                                                    | 54 |

|   |     | 5.4.3 Parser                                                                       | 56 |

|   |     | 5.4.4 Analyzer                                                                     | 59 |

|   | 5.5 | Conclusion                                                                         | 66 |

| 6 | Des | gn Exploration Method                                                              | 69 |

|   | 6.1 |                                                                                    | 69 |

|   | 6.2 | Starting Point                                                                     | 69 |

|   | 6.3 | Task Splitting                                                                     | 70 |

|   | 6.4 | Data Splitting                                                                     | 70 |

|   | 6.5 | Communication Granularity                                                          | 71 |

|   | 6.6 | Data Merging                                                                       | 72 |

|   | 6.7 | Task Merging                                                                       | 72 |

|   | 6.8 | Conclusion                                                                         | 73 |

| 7 | Exp | erimental Results                                                                  | 75 |

|   | 7.1 | Introduction                                                                       | 75 |

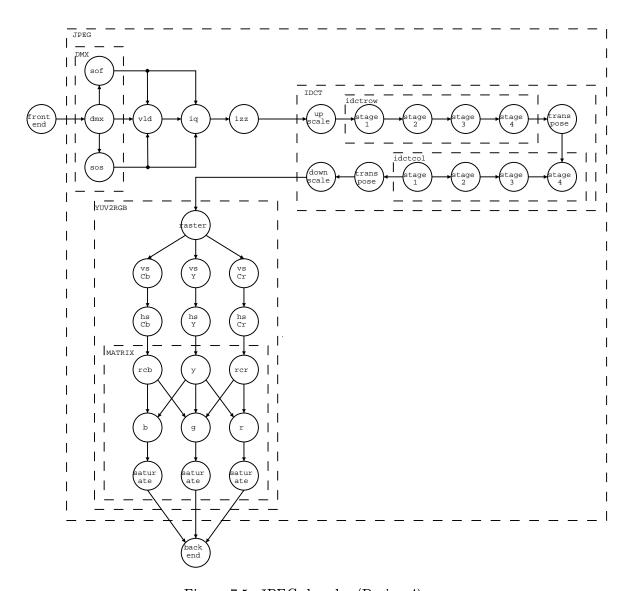

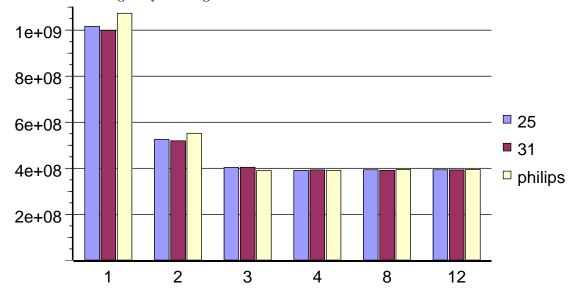

|   | 7.2 | Case Study: JPEG Decoder                                                           | 75 |

|   |     | 7.2.1 Introduction                                                                 | 75 |

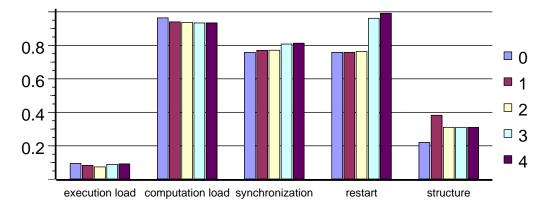

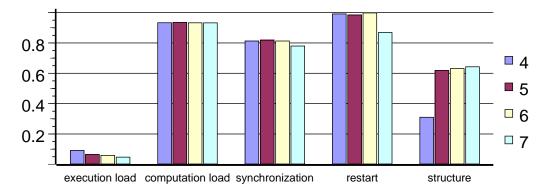

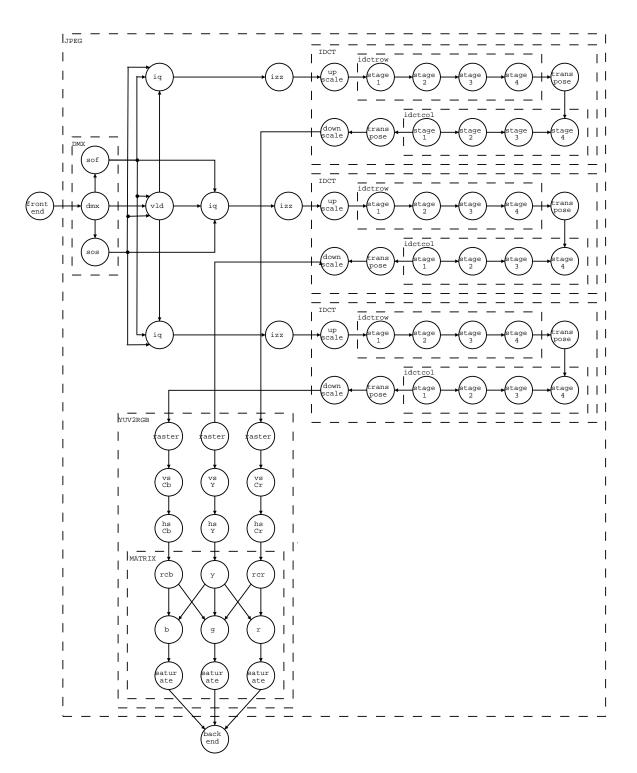

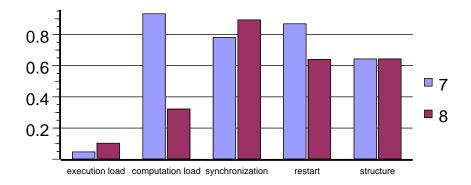

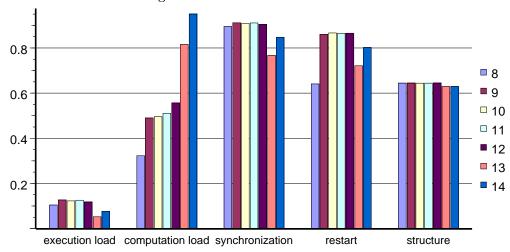

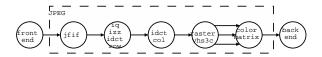

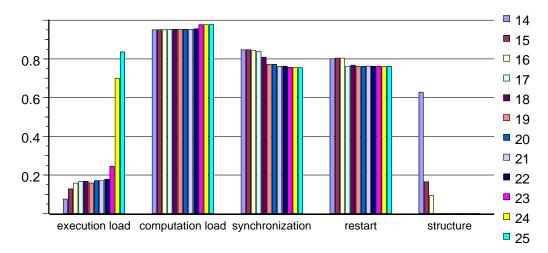

|   |     | 7.2.2 Design Exploration                                                           | 77 |

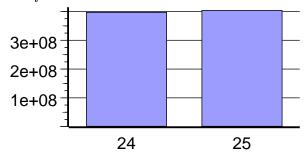

|   |     | 7.2.3 The Effect of the Compiler Used                                              | 90 |

|   |     | 7.2.4 Mapping on a Multi-Processor Platform                                        | 92 |

|   | 7.3 | Conclusion                                                                         | 94 |

| 8 | Con | clusion and Recommendations                                                        | 97 |

| _ | 8.1 | Realized goals                                                                     | 97 |

|   | 8.2 | Recommendations                                                                    | 99 |

|   | Bib | $\log$ raphy                                                                       | 1  |

| A | Con | currency Analysis and Simulation Tool                                              | i  |

| - |     | Introduction                                                                       |    |

|   |     | Command line options $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ |    |

|   | A.3 | Parameters                                                                         |    |

|   |     | Example                                                                            |    |

## Chapter 1

## Introduction

Motivation. Multimedia systems are characterized by an ever-increasing need for compute power. This compute power is needed for the processing of large amounts of data such as images, video and speech. The demand for growing compute power is combined with high energy-efficiency constraints and is satisfied by integrating many average-speed and energy-efficient processing elements on a single chip. The integration of processing elements is resulting in the development of both heterogeneous and homogeneous multi-processor systems. These multi-processor systems are inherently concurrent, as they contain many processing elements that operate in parallel. With a trend toward larger and complexer multi-processor architectures, there will be even more parallelism to exploit. This requires that the parallelism available in an application, which is mapped onto the multi-processor system, is made visible in the mapping trajectory.

A number of different formal models of computation are used in concurrency theory. They express concurrency using formal languages [3], partial orders [30] or automata [7] at different levels of abstraction. Prime examples are Dataflow graphs [23], Petri nets [29] and Kahn process networks [13, 14]. These models of computation make the parallelism in an application visible. They are however not able to answer questions such as: How concurrent is my application? Does the specification maximally exploit the concurrency inherent in the application? How must the specification be modified to better exploit the concurrency in the application? Does the specification optimally exploit the concurrency inherent in the target architecture?

As mentioned, next-generation multi-media systems will use multi-processor architectures to meet the high performance and low energy constraints set by these systems. The concurrency in an application must be made explicit in the specification to exploit the concurrency inherent in these architectures. Such a specification should allow formal reasoning about the concurrency in the application and about how to exploit this concurrency. To date, no formal models exist that are able to do this without fully implementing the system.

This thesis describes a model of computation and accompanying concurrency model that allows formal reasoning about the concurrency in an application without fully implementing the system.

Overview. This thesis is divided in seven main parts: problem definition, model of computation, concurrency model, implementation, design exploration method, experimental results, and conclusions and recommendations. In Chapter 2, we describe the problem definition. Chapter 3 presents a model of computation, namely the model of computational networks, for describing a computation that is performed in a distributed system. A formal concurrency model is presented in Chapter 4. This model can be used to analyze the concurrency in computational networks. In Chapter 5, the implementation of the concurrency model is discussed. A design exploration method that uses the concurrency model is presented in Chapter 6. Chapter 7 demonstrates a design case. This case shows how to convert a computational network into another computational network that better exploits the available concurrency. Finally the conclusions and recommendations are discussed. This includes shortcomings of the concurrency model. Also, further improvements in the software implementation are discussed.

## Chapter 2

## Problem Definition

#### 2.1 Introduction

Future generations of embedded multi-media systems such as hand-held computers, mobile phones, gaming devices, car navigation systems, etc., will have an increasing need for compute platforms that combine high compute power with a low energy consumption. The compute power is needed for the processing of large amounts of data such as images and video, and for applications such as speech recognition and synthesis that can be used to improve user interfaces. The systems must be energy-efficient because they often have only a limited energy supply, typically consisting of a rechargeable battery. Furthermore, a high energy dissipation means that a lot of heat is generated which, in turn, requires a lot of cooling. However, cooling technology takes a lot of space, is relatively expensive, and is susceptible to disturbances.

Engineers are looking for ways to meet both the high compute power and low energy dissipation requirements. One common aspect of many approaches is the exploitation of parallelism in one way or another, as the requirements cannot be achieved via single-processor technology. The following example explains why, and it shows why multi-processor technology can meet the requirements.

**Example 2.1** Consider a system that has to realize a computation (e.g., JPEG or MPEG decoding). The first solution might be to realize this computation using a system that consists of a single processor (single-processor system). This single-processor system has a switching capacitance C, and runs at a supply voltage V with a frequency f. The power dissipation of the single-processor system is equal to:  $P = fCV^2$  [6]. The computation can also be realized using a system with two processors in parallel (multi-processor system). These processors can operate at a frequency f/2. The same amount of work is then still done in the same time as in a single-processor system; assuming the overhead of the multi-processor system is negligible. However, the switching capacitance of the multi-processor system is 2C. The supply voltage of the multi-processor system is V' < V. This voltage can be lower because of the lower switching delay frequency used in the multi-processor system. The power dissipation of the multi-processor

system is then equal to:  $P' = fCV'^2$ .

The ratio between the power dissipation of the multi-processor system and the single-processor system is:

$$\frac{P'}{P} = \frac{fCV'^2}{fCV^2} = \frac{V'^2}{V^2}$$

The power dissipation of the multi-processor system drops with the square of the difference between the voltage of the multi- and single-processor. Note that both solutions have the same compute power, but only a different energy consumption.

This example shows that when a multi-processor system is used, the energy consumption is reduced. A multi-processor system realizes in this way the low energy constraints imposed by future embedded multi-media systems. It can also full-fill the need for high compute power by using enough processors in the system. The single-processor technology can meet the high compute power constraint, but this comes with a higher energy consumption than in the multi-processor solution.

There is, besides the high compute power and low energy dissipation constraint, another reason for considering concurrency. This is the wiring delay problem [27], the delay introduced by on-chip wiring is getting so large in future IC designs that only a very small percentage of the die will be reachable during a single clock cycle. The whole die can as a result no longer be used for one single processor. Locality must be introduced in the architecture to be able to use the whole die. Locality means that a lot of processors will be integrated on a single die. This results in multi-processor systems-on-chip.

The trends described above will lead to systems in which a lot of parallelism is available. The important question is now how this parallelism can be exploited. This requires that the concurrency in the application is made explicit and is adapted to the parallelism in the multi-processor system onto which it is mapped. To solve this problem, we have to answer three questions. First, what do future system architectures look like? Second, how can the concurrency in an application be made explicit without the need to fully implement the system? Third, how do we map a specification onto a multi-processor system? Section 2.2 tries to answer the first question by describing the trends in modern system architectures. Section 2.3 describes the problems that arise when the second question is answered. The third question, the problem of multi-processor mapping is discussed in Section 2.4.

### 2.2 System Architectures

Modern system architectures try to exploit parallelism in one way or another. Good examples are instruction-level parallelism (ILP) in super-scalar and very-long-instruction-word (VLIW) processors and data-level parallelism (DLP) and task-level parallelism (TLP) in (multi-)processor architectures. ILP generally concerns general purpose CPUs, DLP is most common used for both single processor and multi-processor architectures,

and TLP for multi-processor architectures. In the multi-processor approach a system is constructed out of a number of coarse-grain components working together to get the job done. This leads to both heterogeneous [35] and homogeneous [34] multi-processor systems.

The previous section shows that in order to meet the high compute power and low energy consumption constraints of next generation embedded multi-media systems, multi-processors systems must be used. These systems are in nature concurrent. This concurrency must be exploited. This requires that task- and data-level parallelism is used as these allow to execute different parts of a computation concurrently on different processors.

### 2.3 Application Specification

Next-generation embedded multi-media systems will often realize so-called streaming applications in which data transformations play a dominant role (such as video processing). Programming techniques are required to model the functional behavior and desired timing- and energy-related properties of these applications. The previous section shows that these applications will be executed on multi-processor systems. To use these systems, they must be able to exploit the task- and data-level parallelism in the application. This requires that the parallelism in the application is specified, so that it can be used in the multi-processor system.

To model the functional behavior and desired timing- and energy-related properties of these applications, novel programming techniques are required. These programming techniques should provide insight in concurrency-, timing-, and energy-related properties of a system at the specification level, without the need to fully implement an application. An important aspect of these programming techniques is that they must be able to specify the concurrency in an application and allow formal reasoning about it. The next chapter presents a programming technique, the computational-network model, that can be used to explicitly specify the concurrency in an application at the specification level. This model is based on the existing Kahn process network model [13, 14]. The computational-network model is extended with a concurrency model, which makes it possible to reason formally about the task- and data-level parallelism in an application.

### 2.4 Multi-Processor Mapping

Section 2.2 discussed the trends in modern systems architectures. These systems will be multi-processors systems that contain concurrency. Section 2.3 discussed that in order to exploit this concurrency, it must be extracted from the application and made explicit in the specification. One of the important issues facing modern multi-processor designers is now the development of effective techniques for the distribution of the specified, concurrent program over multiple processors. These techniques must optimize execution time, memory usage, and energy consumption.

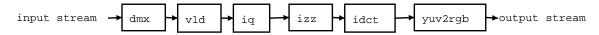

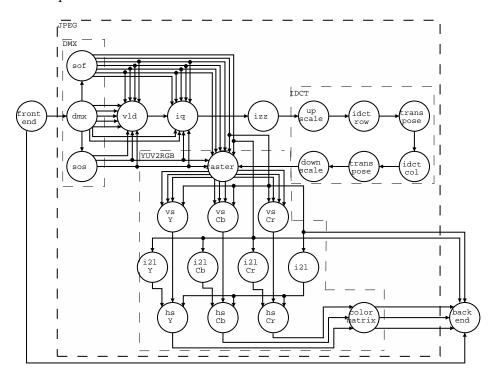

Research on mapping abstract models of computation (e.g. Kahn process networks) onto

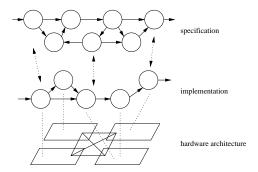

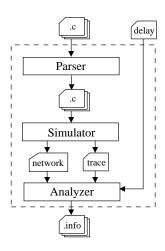

multi-processor systems is still in a very early state [8, 40]. A good example of this is a JPEG case study performed at Philips Research [18]. The article describes a JPEG decoder that is mapped onto a multi-processor system. The techniques used in this case study require that the target architecture is known before the mapping is started. A simulation model of the system architecture is needed in the complete mapping trajectory to verify that the mapping is optimal. This makes that the used techniques are only valid for a given architecture. It also requires extensive simulation, which make the design exploration expensive. To overcome these problems, we think that a global framework needed to do this mapping looks like the mapping trajectory shown in Figure 2.1.

Figure 2.1: Mapping

The mapping trajectory starts with a computational network that specifies the behavior of the application. This computational network is mapped onto an implementation. The implementation is also a computational network. The difference between the specification and the implementation computational network is that the former is to a large extent target-architecture independent, whereas the latter takes all the relevant aspects of a given architecture into account, and is optimized toward desirable properties concerning execution time, power dissipation, etc. The final step is a mapping from the implementation to the hardware architecture. It concerns the efficient execution of sequential code on various sorts of processing elements and is covered by compiler technology.

### 2.5 Motivating Example

In the introduction of this chapter it is stated that future embedded multi-media systems use multi-processor architectures. The trends in these architectures and the required programming and mapping techniques for them are discussed in the previous sections. One of the important messages of these sections is that concurrency must be made explicit in the specification of an application. The granularity of the concurrency in the specification must be adapted to the concurrency available in the system architecture to provide a good mapping. To be able to do this, a model is needed that allows formal reasoning about the concurrency in a specification. This section presents an example that illustrates this need for a formal concurrency model. This example serves as our prime motivation to perform the research described in this thesis.

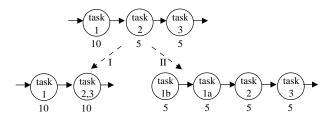

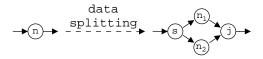

**Example 2.2** Figure 2.2 shows a model for the computation performed by an application. The computation is divided in 3 tasks. These tasks are performed after each other, as indicated by the arrows connecting the tasks. There is an arrow connected to task 1 that is not connected to another task. This models that task 1 gets the data needed to perform its computation, task, from the environment. The arrow leaving task 3 models the output of this task 3. The output produced by task 3 is the output of the computation performed by the application.

Figure 2.2: A computation split in three tasks.

The numbers below the tasks in Figure 2.2 represent the work (e.g. processor time used) of a task when it is executed on a processor for a computation. Section 2.4 stated that at the implementation level there is a specification that can be mapped on a multi-processor system by only considering the efficient execution of sequential code on a processor. This requires that the tasks at the implementation level of the mapping trajectory have a one-to-one mapping with the processors in the system architecture.

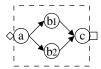

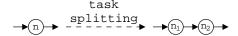

The goal of a multi-processor system will often be to keep all processors busy. As one task is mapped onto one processor, it requires that the total computation is divided evenly over the tasks. In other words, all tasks have to do the same amount of work. The tasks in Figure 2.2 do not meet with this requirement as the first task does the same amount of work as the tasks 2 and 3 together. Figure 2.3 shows two solutions to this problem. Solution I combines the tasks 2 and 3. The two resulting tasks perform both 50% of the work. This solution can be mapped onto 2 processors. The approach used in solution II is different. It does not combine two tasks, but splits task 1 in two new tasks. These tasks 1a and 1b perform both half of the work performed by the original task 1. The tasks in this solution perform all 25% of the total work needed for the computation and would require a multi-processor system with 4 processors.

Figure 2.3: Two solutions with a balanced workload for the computation.

An important question is now which solution, I or II, is better. This will first depend on the systems architecture. If this architecture does not contain 4 processors, then only solution I can be chosen. However if the number of processors in the system architecture is not fixed yet, we can make a trade-off. Solution II will require more processors, more area, than solution I. On the other-side, solution II contains 4 tasks. If these four tasks run on four different processors, then it is possible to let each task execute on a different computation, set of input data. Solution II can then perform its computation on 4 different sets of input data, while solution I can perform in the same time the same computation only on 2 different sets of input data. Solution II has thus a higher throughput. We can thus say that solution II is more concurrent than solution I.

This example shows different that solutions can have different concurrency properties. To compare different solutions, a model of concurrency is needed that allows a system designer to analyze the concurrency in an application in a formal way. This concurrency model must help a system designer in answering questions like: How concurrent is my application? Which of these solutions contains the most concurrency in its specification?

#### 2.6 Conclusion

This chapter shows that concurrency will play an important role in next-generation embedded multi-media systems. These multi-media systems will be multi-processor systems, as that is the only way in which the high-performance and low-power constraints of next-generation compute platforms can be met.

Multi-processor systems are in nature concurrent, and this concurrency in the architecture should be exploited. This requires that the concurrency is used in the mapping trajectory from the system specification to the hardware architecture. The concurrency in an application should therefore be extracted, and made explicit, in the models that are used to specify a system. To support the extraction of concurrency from an application, the model must contain a concurrency model. This concurrency model should support formal reasoning about concurrency. In this way, concurrency can be extracted from an application in a uniform way. To support the designer in the concurrency extraction, the concurrency model must indicate to what extent the concurrency is extracted from an application and it should suggest how the specification of a system must be modified to better exploit the concurrency available in the application.

The next chapter of this thesis presents a model of computation that can be used to specify a system. Concurrency is made explicit in this computational model. Chapter 4 describes a concurrency model that can be used with this computational model and has the above mentioned properties. The rest of this thesis discusses the implementation of the computational model and the concurrency model. It further shows the use of these models in a case study that implements a JPEG decoder.

## Chapter 3

# **Model of Computation**

#### 3.1 Introduction

A number of different formal models of computation are used to model distributed computations. They express concurrency using formal languages [3], partial orders [30] or automata [7] at different levels of abstraction. Prime examples are Dataflow graphs [23], Kahn process networks [13, 14], Petri nets [29], Statecharts [10] and Process Algebra [3]. Section 3.2 introduces a computational model at a higher level of abstraction than these models. The relation with the previously mentioned models is also discussed in this section. Concurrency is made explicit in this model of computation, called the computational-networks model. Section 3.3, extends the computational-networks model with a notion of partially ordered events in time.

### 3.2 Computational Networks

Informally speaking, a parallel computation is organized in the following way: some autonomous computing nodes are connected to each other in a network by point-to-point connections. Computing nodes exchange information through these connections. These connections are the only way by which the computing nodes may communicate. A given node computes on data coming along its input connections to produce output on some or all of its output connections. The computing nodes are at any given time computing or waiting for information on one of their input connections.

Such a parallel computation can be represented as a directed graph. The nodes of this graph represent the computing nodes. The edges represent the communication connections between the computing nodes; an incoming edge represents an input connection, an outgoing edge represents an output connection.

This informal definition of a parallel computation is used to construct the computational-network model. A computing node is modeled in the computational-network model as a compute node. This compute node is a "component" that has a set of input ports and a set of output ports. The input ports hold the input data. This input data is modeled using strings of data-elements. The execution of the compute node can be imagined

by the compute node "reading" or "observing" these input strings and generating the appropriate output strings. This is done following the *transformation* that describes the behavior of the compute node. The output ports will hold the strings after applying the transformation to the input strings. This defines a compute node in an informal way; Definition 3.1 defines a compute node in a computational network in a more formal way.

#### **Definition 3.1 (Compute node)** A compute node is a tuple (I, O, t) where

- i) I is a set of input ports;

- ii) O is a set of output ports;

- iii) t is a transformation. A transformation describes how a compute node computes a (tuple of) strings on its output ports using a (tuple of) strings on its input ports.

A compute node computes a (tuple of) strings on its output ports using a (tuple of) strings on its input ports. These strings are produced and consumed by other compute nodes in the parallel computation or by the environment of the computation. The "communication" of these strings between the different compute nodes is done in the computational-network model using *connections*. Data-streams are transferred in-order over connections.

**Definition 3.2 (Connection)** A connection is a pair (p, q). The connection transfers data-streams in-order (fifo) from port p to port q.

The definition of a compute node and a connection enables us to construct a *network* component. This network component realizes a parallel computation. It contains a set of compute nodes that are connected to each other using connections. The compute nodes in the network component communicate with each other using the connections.

A computation is only useful if the network component will eventually produce a result on some (set of) output port(s). These results are produced on the output port(s) of the compute node(s) in the network component. These output ports must not be connected to the input ports of other compute nodes. The unconnected output ports of the compute nodes serve as the output ports of the network component. A compute node might then communicate its results not only to other compute nodes in the network component, but also to the environment. The parallel computation might also require the use of input from the environment of the network component. The network component should therefore contain a (set of) input port(s). An unconnected input port of a compute node serves then as an input port of the network component. Definition 3.3 defines this network component in a formal way.

# **Definition 3.3 (Network component)** A network component NC is a tuple (N, C, I, O) where

- i) N is a set of compute nodes;

- ii) C is a set of connections;

- iii) Every connection in C connects an output port of a compute node to an input port of a compute node;

- iv) Every port of every compute node is connected to at most one connection;

- v) I is the set of input ports of the network component, being defined as those input ports of the compute nodes in N not connected to a connection in C;

- vi) O is the set of output ports of the network component, being the unconnected output ports of the compute nodes in N.

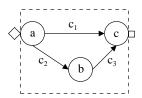

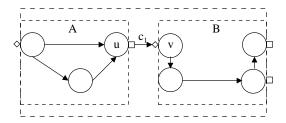

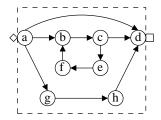

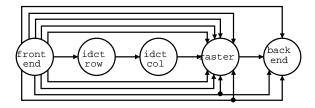

An example of a network component is shown in Figure 3.1. The network component shown here contains three compute nodes a, b and c. They are connected to each other via three connections labeled  $c_1$ ,  $c_2$  and  $c_3$ . The input port of compute node a is unconnected and thus an input port of the network component. This input port is represented by a diamond. An output port of a network component is represented by a small box. Compute node c provides the only output port of this network component.

Figure 3.1: An example of a network component

It is now possible to construct a model for a parallel computation using a single network component. This network component does not contain any hierarchy. Hierarchy might however be useful in a larger computational network, as it allows abstraction from primitive operations taking place in the system. The computation in a network component could be seen as a primitive operation. A parallel computation may consist of the computations taking place in a number of these network components. The network component itself is for the rest of the system a black box with a set of input ports, a set of output ports and a defined behavior i.e., to the outside world it looks like a compute node. Definition 3.4 defines a computational network, which realizes this hierarchy. The definition follows the same lines as Definition 3.3.

**Definition 3.4 (Computational network)** A computational network is defined as a tuple (NC, C, I, O) where

- i) NC is a set of network components;

- ii) C is a set of connections;

- iii) Every connection in C connects an output port of a network component to an input port of a network component;

- iv) Every port of every network component is connected to at most one connection;

- v) I is the set of input ports of the computational network, being defined as those input ports of the network components in NC not connected to a connection in C;

- vi) O is the set of output ports of the computational network, being the unconnected output ports of the network components in NC.

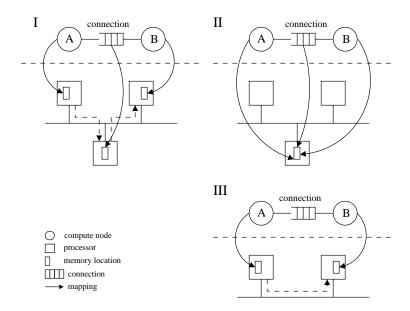

A computational network contains a set of network components that perform computations. The computational network contains further a set of input ports and a set of output ports. These are used to communicate with the outside world. The network components are connected to each other by connections in the computational network. The unconnected input ports and output ports of the network components serve as the input ports and output ports of the computational network. An example of a computational network containing two network components A and B is shown in Figure 3.2. The two network components are connected to each other with the connection  $c_1$ . This connection connects the input port of compute node v in network component B to the output port of compute node v in network component A.

Figure 3.2: An example of a computational network

The combination of Definitions 3.3 and 3.4 gives a modular model of computation that allows two levels of abstraction. It is straightforward to generalize this to a truly hierarchical model by assuming that the compute nodes in a network component can be seen as network components themselves. However, this is not done because it would unnecessarily complicate the remainder.

The concept of the computational-network model introduced in this section is as follows: compute nodes read a (set of) strings from their input ports. These strings are transformed according to the transformation defined by the compute nodes. The result of this transformation is again a number of strings that are written to the output ports of the compute nodes. The compute nodes communicate with each other using connections. Section 3.1 lists a number of formal models of computations that are used to model distributed computations. We now discuss how some of these computational models can be modeled in the computational-networks framework. The first model of computation that was mentioned is the Kahn process networks (KPNs). KPNs are easily modeled in our framework. The functions in KPNs become our compute nodes. The data streams that are used in KPNs to communicate between the functions are realized by sending these streams over the connections in the computational-network model. The computational-network model can also model Dataflow graphs (DFGs). The actors in a DFG become our

3.3. EXECUTIONS

compute nodes and the communication is done using data streams. The computational-network model can further model a subclass of Petri nets, the marked graphs. The transitions in these marked graphs become our compute nodes and the places become the connections.

#### 3.3 Executions

A computational network, which was introduced in the previous section, consists of a set of network components. These network components consist on their turn of a set of compute nodes  $n_1, n_2, \ldots, n_M$  which together perform a computation. Each compute node performs therefore a sequence of actions which are modeled as a totally ordered sequence of events. A compute node can write on its output ports, as a (set of) strings, the result of the transformation performed to the (set of) strings it reads from its input ports.

The events that can occur in a computational network during a computation are classified into the following three types:

- 1. write event Such an event models a write operation in which a compute node writes on one of its output ports;

- 2. **read event** Such an event models a read operation in which a compute node reads from one of its input ports;

- 3. **internal event** Such an event models the execution of an action or a sequence of actions; these actions must not include read or write operations.

The execution of a compute node is a totally ordered sequence of internal, read and write events that take place during the execution of the compute node. The read and write events impose further a partial order on the events taking place in the computational network as a whole. The relation between the different events is called the *causality* relation or happened before relation and denoted by  $\prec$ . The causality relation is defined according to [22].

**Definition 3.5 (Causality relation)** Let E be a set of events produced by the execution of a computational network. For  $e, e' \in E$ ,  $e \prec e'$  holds if and only if

- i) e and e' are events in the same compute node and e precedes e',

- ii) e is a write event and e' is the corresponding read event, or

- iii) there exists an e'' such that  $e \prec e''$  and  $e'' \prec e'$ .

Two events e and e' are said to be causally related if and only if  $e \prec e'$  or  $e' \prec e$  holds. If neither  $e \prec e'$  nor  $e' \prec e$  holds, these events are concurrent. Let  $e_1, e_2, \ldots, e_k$  be a sequence of events such that  $e_i \prec e_{i+1}$  for  $1 \leq i \leq k-1$ . Such a sequence is called a causal path from event  $e_1$  to event  $e_k$ .

In an implementation it makes sense to associate different delays with the different events that can take place in the system. The communication that takes place in the system will also have a delay associated with it. The main idea behind the computational network is that it can model a distributed computation and that it allows reasoning about different aspects of the system. A number of these aspects are influenced by the timing properties of the events that take place in the system and the causal path of the events in the computation. To allow reasoning about causality and some timing aspects on a relative high level of abstraction without referring to implementations/physical time, we use logical clocks. To make it more practical, we introduce delays for the events that take place in compute nodes and delays for the connections.

Lamport's logical clocks [22] can be used to create an ordering that is consistent with causality (Definition 3.5) for all events that occur during a computation in the computational network. Lamport's system of logical clocks assumes a set of logical clocks, one per compute node. The logical clock's assign to every event a time-stamp that contains the value of the logical clock at the moment the event occurred. Every event is performed within a single logical clock value; there is no delay associated with this event. The clock of a node is incremented once between two events. Furthermore, communication imposes a causality relation that must be respected by the logical clock, which means that the clock of a reading node is updated based on the time-stamp of the read event. There is no delay associated with the communication itself.

To reason about timing aspects without referring to implementations, we associate a delay with the events that take place in the compute nodes and the communication over the connections. To model this delay, we extend the Lamport's logical clocks with a function d, called the *delay function*. This function associates a delay with every event that occurs during a computation in the computational network.

Formally, the delay function maps a set of events E plus the set of connections C to the set of natural numbers, denoted  $\mathbb{N}$ . Formally,  $d:E\cup C\to \mathbb{N}$ . The Lamport's logical clocks can be modeled by assigning a delay of one to every event and a delay of zero to every connection.

The time-stamping mechanism based on Lamport's logical clocks, in the remainder simply referred to as the time-stamping mechanism, contains a function t. It is called the global logical clock and maps a set of events E to a totally ordered set  $\mathbb{N}$  with ordering  $\langle \cdot \rangle$ . Formally,  $t: E \to \mathbb{N}$  such that  $e \prec e' \Rightarrow t(e) < t(e')$ . The global logical clock can be computed via a set of counters, the local logical clocks. Each compute node in the computational network maintains a different counter. Let  $t_i$  denote the counter maintained by compute node  $n_i$ .

When a compute node  $n_i$  executes an event, it updates first its local clock  $t_i$  and then assigns a time-stamp t to the event. This time-stamp is the value of the local logical clock after the event is executed.

The protocol used to update the clock  $t_i$  of a compute node  $n_i$  is the following:

1. When  $n_i$  executes an internal event or a write event e, the clock value  $t_i$  is advanced by setting  $t_i := t_i + d(e)$ .

3.3. EXECUTIONS

2. When  $n_i$  executes a read event e, where y is the time-stamp of the corresponding write event and  $c_j$  is the connection over which the event was received. The clock is advanced by setting  $t_i := \max(t_i, t + d(c_i)) + d(e)$ .

The local logical clock change depends in case 1 of the protocol only on the delay associated with the event executed. The change of the local logical clock in case 2 of the protocol is more complex. It is of course determined by the delay associated with a read event, but also by the causality relation imposed by the corresponding write event and the delay associated with the connection. If the logical clock of the compute node is already larger than the logical clock value of the compute node in which the write event occurred at the time of this write event plus the delay associated with the channel, then the logical clock is advanced by the delay associated with the read event. Otherwise, the logical clock of the compute node is changed to the value of the logical clock of the compute node at the time the corresponding write event occurred. This logical clock value is then raised by the delay associated with the connection and the read event.

The time-stamping mechanism based on Lamport's logical clocks provides a method for deriving an ordering of all events that take place during a computation in the computational network. This ordering is consistent with causality and the delay associated with the events that take place in the computation. The time-stamping mechanism can be used to analyze the ordering and abstract timing of events that take place in a computation. The remaining part of this section introduces a number of measures, based on the time-stamping mechanism. The measures represent a number of timing related properties of a computation in a computational network.

First, we define the execution time (Definition 3.6) of a compute node and the total execution time (Definition 3.7) of a computational network. The execution time of a compute node represents the amount of logical time that a compute node is executing for a computation. The duration of the total computation in the computational network is expressed in the total execution time.

**Definition 3.6 (Execution time)** The execution time,  $T_e^n$ , of a compute node n in which the set of events  $E_n$  occurs, is defined by Equation 3.1.

$$T_e^n = \sum_{e \in E_n} d(e) \tag{3.1}$$

**Definition 3.7 (Total execution time)** The total execution time,  $T_E$ , is defined as the time needed for an execution. In other words, the total execution time is equal to the largest value of the local logical clocks of all compute nodes at the end of the execution.

The execution time of a compute node indicates how long, expressed in logical time, the compute node was running. The total execution time measures how much time was needed to execute the complete computation on the computational network. A compute node need not be executing during the total execution time. The compute node may be idle because it has finished its execution or it is waiting for data on one of its input ports. The *idle time* of a compute node is defined as follows:

**Definition 3.8 (Idle time)** The idle-time,  $T_i^n$ , of a compute node n is defined by Equation 3.2.

$$T_i^n = T_E - T_e^n (3.2)$$

An executing compute node performs read, write and internal events. The read and write events are needed to communicate with other compute nodes. The internal events are needed to perform the transformation of the compute node. This transformation can be seen as the computation performed by the compute node on the data read on its input ports. The logical time needed to perform this transformation is expressed in the computation time (see Definition 3.9).

**Definition 3.9 (Computation time)** The computation time,  $T_c^n$ , of a compute node n in which the set of internal events  $I_n$  occurs, is defined by Equation 3.3.

$$T_c^n = \sum_{e \in I_n} d(e) \tag{3.3}$$

In the remainder of this thesis we use the word *computation* exclusively for the transformations performed on the strings of data in the network. This does not include the communication of the strings of data. When we refer to the combination of computation and communication we use the word *execution*. The computation performed by a compute node refers thus to the internal events that have occurred in the node to perform the transformation. The execution of a compute node refers to the combination of internal, read and write events that occur in a node.

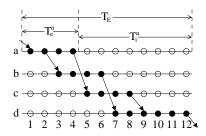

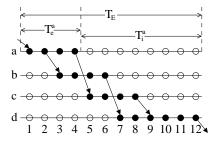

A computation can be displayed graphically in an event diagram, such as the one shown in Figure 3.3. There are four compute nodes a, b, c and d in this figure. The clock ticks at which a read, write or internal event is occurring are indicated by black circles with respectively an arrow leaving it, entering it or with no arrow connected to it. An event that takes more clocks ticks is indicated by a black ellipse over all clock ticks at which the event occurred. An arrow indicating a read or write event is connected to the first clock tick at which the event occurred. In Figure 3.3 we have Lamport's logical clocks, i.e., d(e) = 1 for event e and d(c) = 0 for connection c. At logical time 1, there occurs a read event in compute node a, this is a read event in which the compute node reads data from the environment – outside world. This is represented by a black circle with an arrow entering it, just as in a normal read operation. But the other side of the arrow is not connected to another event in the event diagram, this indicates that it is a read from the environment. A write to the environment is represented by an arrow leaving a black circle but not entering another black circle. Such a write event can be seen at logical time 12 in compute node d. The total execution time of this computational network is equal to 12, as at that logical clock value the last event occurs. The compute node a has an execution time of 4, an idle-time of 8 and a computation time of 2.

Figure 3.3: Example of an event diagram

As explained, the idle-time  $T_i^n$  represents the logical clock values at which no event is being executed in a compute node  $n_i$ . The node is said to be *idle* at these clock values. The clock value at which this occurs is called an *idle time* of the node. Idle times are represented in Figure 3.3 by unfilled circles.

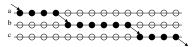

Figure 3.4: Idle events in a compute nodes

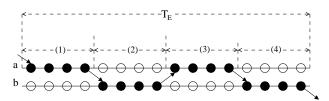

Figure 3.4 shows the event-time diagram for a computation in a computational network that consists of two compute nodes a and b. It shows all the computation needed for a single input from the environment. Compute node a performs events at the logical clock values 1 through 4 (period (1)) and from 9 through 12 (3). The compute node is idle from the logical clock values 5 through 8 (2) and from 13 through 16 (4). The reason for the compute node being idle in period (2) and (4) is different. In (2), the compute node is waiting for data from compute node b. In (4), the compute node has finished its execution, while the computation has not yet finished. Another execution of compute node a for a new input could already start during period (4). This is a desired property as we are aiming at streaming applications in which the same computation must be repeated many times on different inputs. Starting another computation is not possible during period (2), as the execution has not yet finished. The idle time of period (2) is unavoidable in the computation – the compute node cannot execute for this computation or another computation –, while the idle time of period (4) is not. The question is now what causes the idle time and whether or not the idle time is unavoidable in the computation. To answer the first question, we have to see why an idle time can be present:

- 1. The execution of a compute node n is not started yet, but the computation is;

- 2. The execution of a compute node n is finished, but the computation is not;

- 3. The execution of a read event of a compute node n is delayed because the required data from another compute node is not yet available.

The idle time caused by case 3 is important for the behavior of the computational network and should be removed to get a more concurrent solution. It may be possible to remove this idle time by changing the order of events in the causal chain(s) leading through the read event causing the problem. The idle time caused by cases 1 and 2 are not important for the computational network, as those idle times will be used for the execution of the compute node for another input. To make a distinction between the idle time that is important for the computational network and the idle time that is not important, we introduce the *communication idle time* (Definition 3.10). This communication idle time is equal to the idle time caused by case 3.

**Definition 3.10 (Communication idle time)** The communication idle time,  $T_{ci}^n$ , of a compute node n is defined as the number of idle times of n after the first read or write event occurred and before the last read event occurred.

The time that a computation occupies a compute node, the node cannot execute for another input, is called the *run-time*. This time includes the execution time (see Definition 3.6) and communication idle time (see Definition 3.10) of a compute node, as those two times together determine the number of logical clock values at which the compute node is occupied by a computation.

**Definition 3.11 (Run-time)** The run-time,  $T_r^n$ , of a compute node n is given by Equation 3.4.

$$T_r^n = T_e^n + T_{ci}^n \tag{3.4}$$

The last measure that is defined is the sequential execution time.

**Definition 3.12 (Sequential execution time)** The sequential time of an execution,  $T_{SE}$ , is the time needed to run the computation sequentially. This time is defined to be equal to the sum of the execution times of all compute nodes in the computational network:

$$T_{SE} = \sum_{n} T_e^n \tag{3.5}$$

The sequential execution time is found by adding the execution times of all compute nodes in the computational network. This approximates the execution time of a sequential version of the computation. This approximation is in general not exact, as a sequential execution might have different delays associated with the read and write events, as these transform into local variable operations. There will also be control statements needed in the sequential execution to perform the correct computation. This will introduce some extra delay. It is however assumed that the sum of the execution times will be a reasonable measure of the execution time of a sequential version of the computation.

#### 3.4 Conclusion

This chapter has presented a model of computation that can be used to model distributed computations. This model is comprised of two parts. The first part, the computational-network model, can be used to specify a concurrent system. The second part models executions and can be used to analyze the events that take place during a single execution.

The computational-network model operates at a high level of abstraction. This allows the modeling of all kinds of different properties of systems in a very natural way. The computational-network model introduces a natural way to explicitly specify concurrency in a system by introducing different compute nodes in a computational network. These compute nodes communicate with each other by means of connections. The computational networks model allows for the modeling of different models of computation in its framework.

Section 3.3 has introduced a classification for the different events that can occur in a distributed computation and introduces the causality relation among these events. These events can be ordered using a time-stamping mechanism based on Lamport's logical clocks. This time-stamping mechanism gives an ordering of the events taking place in a distributed computation and introduces an abstract notion of time into the computational-network model. The notion of time is extended with a number of different time measures that express the activity of a compute node and the computation.

The remainder of this thesis studies a formal concurrency model that is based on the computational-network model and the notion of time which have been introduced in this chapter.

## Chapter 4

# Concurrency Model

#### 4.1 Introduction

The previous chapter introduced the computational-network model. In this model, autonomous computing nodes are modeled as compute nodes, which communicate with each other using point-to-point connections. The compute nodes perform a concurrent computation on the data. Concurrency in the computation is made explicit in this way. This chapter describes a formal concurrency model that can be used to analyze the concurrency in a computational network. Section 4.2 discusses the basic assumptions that are made in the concurrency model about the computational network. Section 4.3 presents the concurrency model that is comprised of five main measures supported by a set of detailed measures. A set of computational networks analyzed using the concurrency model is presented in Section 4.4. The relation with other concurrency models is discussed in Section 4.5 Finally, Section 4.6 contains some concluding remarks.

### 4.2 Assumptions

Concurrency in a computational network is influenced by many things. It is for instance influenced by the way the computation is divided over the different compute nodes in the computational network. If all compute nodes have to do more or less the same amount of work for a computation, then it might be possible to do much of the computation concurrently. If not, then a small number of the compute nodes has to do most of the job, while the other compute nodes are idle (not executing). It will be clear that in the latter case there is less concurrent activity possible in the computational network. This concurrency property is one of those that we are interested in, because changes in the computational network may influence it. Therefore, it will be taken into account in the concurrency model that is presented in the next section.

The communication structure may also influence the concurrency in the computational network. This can happen in a number of ways. First, the length of the string of data that can be present on a connection at one moment in time may influence it. Assuming a connection can hold only a string of data of finite length, then a write event may be

blocked because a connection is full. This will influence the concurrency, as the compute node cannot continue its computation until there is enough space on the connection to complete the write event. This effect is caused by the amount of memory allocated for the connection [2] and not by the computational network itself. This effect from the environment should not be taken into account in the concurrency model. It can be left out with the following assumption.

**Assumption 4.1** The strings of data on the connections of the computational network may be of infinite length.

A compute node can also be blocked if it cannot read the data from its input ports. If these input ports are connected to the environment, then it implies that the compute node must wait until the environment has written the data to the connection. As we do not want to study the effects of the environment on the concurrent behavior of the computational network, this should not be possible. This is realized using the following assumption.

**Assumption 4.2** The strings of data on the input ports of the computational network are of infinite length. These strings of data are infinite concatenations of the strings of data required for one computation and are present on the connection before the connected compute node wants to read them.

This assumption implies that the computational network performs infinitely many times the same computation on the same data set. In this way, it is possible to analyze the behavior of the computational network as if it is running on an infinitely large set of inputs. These inputs are all the same. In practice, this will not be true. I.e., a JPEG decoder will decode a set of different images. The images need not be the same. However, their data streams will be comparable. It is the idea that the input used in our assumption approximates the average input of the computational network.

The concurrency is also influenced by the mapping of compute nodes on processors. The nodes of a network will be executed on a set of processors. A (run-time) scheduler will assign the nodes to processors on which they execute. If there are less processors than compute nodes, the scheduler will have to choose which compute node to execute when. This effect is caused by the environment – the (run-time) scheduler – and not by the computational network itself. We are not interested in effects on the concurrency that are caused by the environment. They must therefore be left out of the concurrency analysis. This is done using the following assumption.

**Assumption 4.3** There are infinitely many processing nodes available.

This assumption implies that a compute node that wants to execute can do this as soon as the required data becomes available. Only the absence of required data on its input ports can stop a compute node from executing. Effects of scheduling a compute node on a processor are in this way left out of the model.

The final assumption that is made is the following.

**Assumption 4.4** The computation time of a single computation is finite.

This assumption implies that the strings of data for one computation, which are present at the input ports of the computational network, are of finite length. This makes it possible to analyze, in finite time, the behavior of the computational network.

### 4.3 Concurrency Measures

A computational network that realizes a computation has certain concurrency properties. The goal of the concurrency model is to provide measures for these properties. To be able to derive these measures, we must first identify which properties must be considered. To do that, we consider what a computational network does. In short: a computational network performs a transformation on the data streams communicated over the connections. The compute nodes in the computational network are busy with the computation – applying transformation – and communication – reading and writing to the connections. Considering concurrency, we want that all compute node have to do an equal share of the computation. This balanced workload provides the option to have a low scheduling overhead. The compute nodes must also perform the computation as fast as possible – each compute node individually and the computational network as a whole. Finally, it is required that not too much of the time is spent on communication. To get numerical values for all of these properties, we introduce five different concurrency measures in the following sections. Each section treats one measure. It explains which concurrency property the measure captures, why it is needed and how the measure must be interpreted. An important goal for the concurrency measures is that the values are in the range [0,1], in which a value 1 means that the measured concurrency property is optimal and a value close to 0 means that it is very bad. This makes it simple to compare different computational networks.

In the remainder it is assumed that CN = (NC, C, I, O) is a computational network with NC a set of network components and C a set of connections. nc = (N, C, I, O) denotes a network component in NC and n is a compute node in the network component nc.

#### 4.3.1 Computation Load

A computational network consists of a set of compute nodes that communicate with each other. Each compute node performs a transformation on the data it reads from its input ports. The result of this transformation is written to the output ports of the compute node. The transformation can be seen as the computation performed on the data by the compute node. The compute node will need a certain amount of time to perform this computation. The compute node will also need a certain amount of time to communicate the data with other compute nodes.

The goal of a computational network is that the strings of data that are on the input ports of the computational network are transformed into strings of data on the output ports of the computational network. This transformation should be done efficiently. This means that all of the compute nodes working must spend as much effort as possible on computing the result. This implies that every compute node should spend a large amount of its time on the computation and not on communication.

One could argue that introducing more compute nodes may result in the possibility to do more of the transformation in parallel. This would then lead to a faster transformation of the strings of data. However, communication takes time and this time needed for communication may outweigh the time gained by splitting compute nodes.

We can conclude from the observations presented above, that the ratio between the time spent on computation and the time spent on communication is important when considering concurrency. This observation leads to the first measure in the concurrency model, the *computation load*.

The computation load has to express the ratio between the time spent on the transformation and the time spent on the transformation and communication together. This ratio can easily be computed for a single compute node. The time spent on the transformation is then expressed by the computation time of the compute node (see Definition 3.9). The time needed for both the transformation and communication is expressed by the execution time (see Definition 3.6). The computation load of a compute node n is then given by Equation 4.1.

$$computation load_n = \frac{T_c^n}{T_e^n}$$

(4.1)

The value of the computation load is in the range [0,1]. A value of 1 means that the compute node is all of its time busy with the transformation, while it does not spent time on the communication. A value of 0 means on the other hand that all of the time is spent on communication.

To get a value for the computation load of a network component, we take the average computation load of the compute nodes in the network component nc (See Equation 4.2). In this way, we get a notion of the time spent on the transformations in the compute nodes compared to the time they spent on transforming and communicating the strings of data.

$$computation \ load_{nc} = \frac{\sum_{n \in N} computation \ load_{n}}{|compute \ nodes \ in \ nc|}$$

(4.2)

Equation 4.2 associates a computation load with a network component as defined in Definition 3.3. A computational network consists of a set of network components. To get a computation load for the computational network, we could simply take the average computation load of the network components. The problem with this solution is that the average is taken over the network components without considering the number of compute nodes in a network component. The number of compute nodes in a network component does not influence the measure. This is not a desired property. Consider for instance the situation in which a computational network contains two network components. One has a computation load of almost 1 and contains 10 compute nodes. The other network

component contains only 1 compute node and has a computation load of almost 0. If the computation load of the computational network is calculated by taking the average over the computation loads of the network components, then it would have a value of around 0.5. We might conclude from this that the compute nodes spend on average as much time on the transformation, as they spend on the communication. This is obviously not true, as most of the compute nodes spend almost all of there time on the transformation. In this way, it would be possible to regroup the compute nodes over the network components and obtain different numbers. This does not make sense, as the time spent on the communication and transformation of each compute node and the computational network as a whole does not change.

It will be clear that the number of compute nodes in a network component must be taken into account, when computing the computation load of a computational network. Therefore, we associate with each network component a *size*. The size of a network component is equal to the number of compute nodes in the network component (See Equation 4.3).

The computation load of the computational network is given by Equation 4.4. This measure weights the computation load of the network components by their size.

$$size_{nc} = |compute\ nodes\ in\ nc|$$

(4.3)

$$computation \ load = \frac{\sum_{nc \in NC} computation \ load_{nc} \cdot size_{nc}}{\sum_{nc \in NC} size_{nc}}$$

(4.4)

The main concurrency measure in the concurrency model is the computation load measure of a computational network (Equation 4.4). The computation load measures for the network component (Equation 4.2) and compute node (Equation 4.1) are so called detailed concurrency measures. These detailed measures provides an insight in the concurrency properties of the different network components and compute nodes.

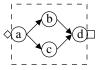

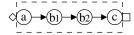

**Example 4.1** Given the computational network of Figure 4.1. This computational network consists of one network component. The network component contains four compute nodes a, b, c and d.

Figure 4.1: Computational network

The computation performed by this computational network starts with compute node a that reads data from its input port. It performs a transformation on this data. The result is written to its output ports, that are connected to the input ports of the compute nodes

b and c. These compute nodes read the data output by compute node a from their input ports, apply a transformation to it and write the result to their output ports. Compute node d will then read these strings of data and perform also a transformation on it. The results of this transformation are output by compute node d and the computational network, as the output port of compute node d is the output port of the computational network.

The event diagram for this computation is shown in Figure 4.2.

Figure 4.2: Event diagram

The event diagram shows that all compute nodes have idle time. For instance, compute node a has an idle-time of 8 logical clock values. This idle-time does not belong to the communication idle time (see Definition 3.10). As all idle-time for a occurs after the last write event. The idle time of all other compute nodes is also no communication idle time. These compute nodes idle before the first read event and after the last write event. The computation load of the compute nodes is found using Equation 4.1 and is listed in Table 4.1.

| compute node | computation load |  |

|--------------|------------------|--|

| a            | 0.25             |  |

| b            | 0.5              |  |

| $\mathbf{c}$ | 0.5              |  |

| d            | 0.5              |  |

Table 4.1: Computation load of compute nodes.

The computation load of the computational network is now found using Equation 4.4. The result is listed in Table 4.2.

| measure          | value |

|------------------|-------|

| computation load | 0.44  |

Table 4.2: Computation load of computational network.

The value of the computation load indicates that the compute nodes in the computational network spent almost the same amount of time on performing the transformation as they spent on communication.

#### 4.3.2 Execution Load

The computation load measure came from the observation that there must be a balance between the time spent on the transformation in the compute nodes and the time spent on communication between the compute nodes. The measure compares the number of internal events to the total number of internal, read and write events that occur during the execution of a transformation in a compute node. The measure does not consider that a compute node may also be idle as it is waiting for data on its input ports. This idle time has been called the communication idle-time (see Definition 3.10) in the previous chapter. It will be clear that in the optimal situation there is no communication idle-time. This might however not always be possible, but the communication idle-time should always be as low as possible. This observation leads to the introduction of the second measure in the concurrency model, the execution load.

The execution load must express the ratio between the time that a compute node is busy compared to the time that a compute node must wait. This ratio can easily be computed for a single compute node. The time that a compute node is busy is expressed by the execution time of the compute node (see Definition 3.6). The total time needed by a compute node is given by the run-time (see Definition 3.11). This run-time takes both the execution time and communication idle-time into account. The execution load of a compute node n is given by Equation 4.5.

$$execution \ load_n = \frac{T_e^n}{T_r^n} \tag{4.5}$$

The value of the execution load is in the range (0,1] assuming that at least one event occurs in a node. A value of 1 means that the compute node does not idle during its execution; it does not have to wait for data. A value close to 0 means that the compute node is almost all of its time waiting for data produced by other compute nodes.

To compute the execution load of a network component, we could follow the same approach as with the computation load and take the average execution load of the compute nodes in the network component. We would then ignore the fact that a compute node may have to idle before it can start a new transformation on a new set of data-strings because the compute node is faster than another compute node. To explain this, we must consider Assumption 4.2. This assumption says that the computational network must perform the same computation infinitely many times. Each compute node inside the computational network will perform the same events in the same order for every computation, as the input for every computation is the same. Therefore, the execution-time of every compute node will be the same for every computation. Consider now the situation in which two compute nodes a and b have a run-time of respectively 10 and 20 time-units and their executions depend on each other. If both compute nodes are executed for 10 computations, then a executes for 100 time-units, while b executes for 200 time-units. One could then be tempted to say that a has finished these 10 computations much earlier than b. But if infinitely many computations are run, they will require both infinite

time-units to execute. The time required for a single computation is for compute node a still half of the time required for compute node b. This can be seen as that compute node a has to wait after each computation until compute node b is finished. Compute node b is thus adding extra idle-time to the execution of compute node a. This example shows that if infinitely many computations are executed and a compute node does not have the longest run-time of all compute nodes in the computational network, it will have to idle before it can start a new computation.

This leads to the conclusion that the rate at with subsequent computations can be started is determined by the slowest compute node i.e., compute node with longest runtime. This longest run-time is called the *run-time of the network component* and is given by Equation 4.6.

$$T_r^{nc} = \max_{n \in N} T_r^n \tag{4.6}$$

To compute the execution load of a network component, we must scale the execution loads of the compute nodes inside the network component with their run-time compared to the run-time of the network component. In this way, we take the fact that compute nodes may have to idle before subsequent computation into account. The execution load of a network component nc is given by Equation 4.7.

$$execution \ load_{nc} = \frac{\sum_{n \in N} execution \ load_n \cdot \frac{T_r^n}{T_r^{nc}}}{size_{nc}}$$

(4.7)

Using the execution load of a compute node (see Equation 4.5) and the run-time of the network component (see Equation 4.6), we get Equation 4.8 for the execution load of a network component nc.

$$execution \ load_{nc} = \frac{\sum_{n \in N} \frac{T_e^n}{T_r^n} \cdot \frac{T_r^n}{T_r^{nc}}}{size_{nc}} = \frac{\sum_{n \in N} T_e^n}{size_{nc} \cdot \max_{n \in N} T_r^n}$$

(4.8)

The execution load measures takes in this way the average of the time that compute nodes are performing internal, read and write events during a computation. It indicates how well the workload (transformation and communication) is balanced over the different compute nodes in the network component. This execution load balance should be as high as possible, as that means that all compute nodes need around the same time to finish their work.

**Example 4.2** We continue with the previous example (Example 4.1). The execution load of the compute nodes is found using Equation 4.5. It is listed in Table 4.3.

| compute node | execution load |

|--------------|----------------|

| $\mathbf{a}$ | 1              |

| b            | 1              |

| $\mathbf{c}$ | 1              |

| $\mathrm{d}$ | 1              |

Table 4.3: Execution load of compute nodes.

All compute nodes have an execution load of 1. This indicates that a compute node does not have to wait for data of other nodes when it can start executing, it has no communication idle time. A compute node may have to idle before it can start a new computation. Because of that, we must scale the execution load of the compute nodes when the execution load of a network component is calculated. This scaled execution load is given by Equation 4.9. The scaled execution load of the compute nodes in the network component are shown in Table 4.4.

$$scaled\ execution\ load_n = execution\ load_n \cdot \frac{T_r^n}{T_r^{nc}}$$

$$(4.9)$$

| compute node | scaled execution load |

|--------------|-----------------------|

| a            | 0.66                  |

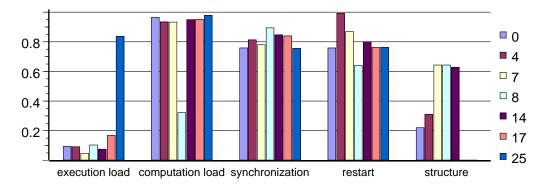

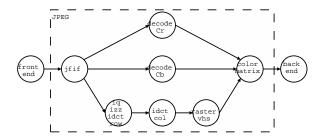

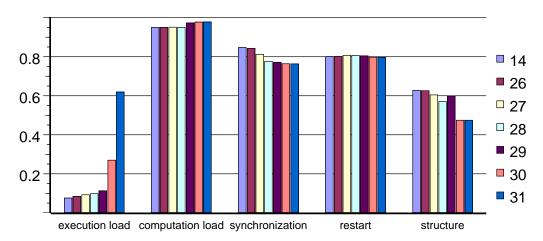

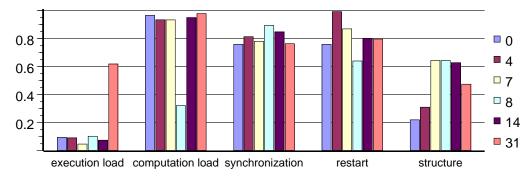

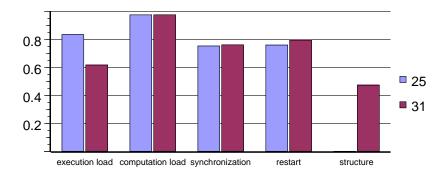

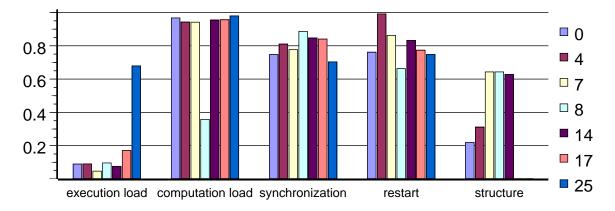

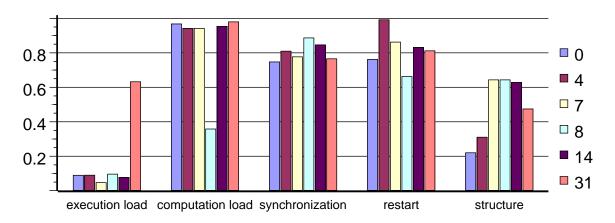

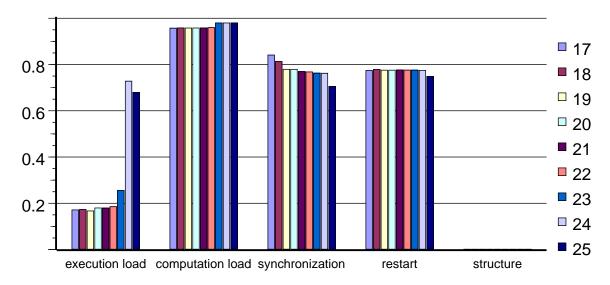

| b            | 0.66                  |