# Predictable Mapping of Streaming Applications on Multiprocessors

## PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op donderdag 25 oktober 2007 om 16.00 uur

$\operatorname{door}$

Sander Stuijk

geboren te Breda

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. H. Corporaal en prof.dr.ir. J. van Meerbergen

Copromotor: dr.ir. T. Basten

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Stuijk, Sander

Predictable Mapping of Streaming Applications on Multiprocessors

/ by Sander Stuijk. - Eindhoven : Technische Universiteit Eindhoven, 2007.

Proefschrift. - ISBN 978-90-386-1624-7

NUR 959

Trefw.: multiprogrammeren / elektronica ; ontwerpen / multiprocessoren / ingebedde systemen.

Subject headings: data flow graphs / electronic design automation / multiprocessing systems / embedded systems.

Predictable Mapping of Streaming Applications on Multiprocessors Committee:

prof.dr. H. Corporaal (promotor, TU Eindhoven) prof.dr. J. van Meerbergen (promotor, TU Eindhoven) dr.ir. T. Basten (copromotor, TU Eindhoven) prof.dr. K.G.W. Goossens (TU Delft) prof.dr. A. Jantsch (Royal Institute of Technology, Kista, Sweden) dr. R. Marculescu (Carnegie Mellon University, Pittsburgh, USA) prof.dr.ir. R.H.J.M. Otten (TU Eindhoven)

The work in this thesis is supported by the Dutch government in their NWO research program within the PROMES project 612.064.206.

This work was carried out in the ASCI graduate school. ASCI dissertation series number 152.

iPhone is a registered trademark of Apple Inc. PlayStation3 is a registered trademark of Sony Computer Entertainment Inc.

<sup>©</sup> Sander Stuijk 2007. All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Printing: Printservice Technische Universiteit Eindhoven

# Abstract

#### Predictable Mapping of Streaming Applications on Multiprocessors

The design of new consumer electronics devices is getting more and more complex as more functionality is integrated into these devices. To manage the design complexity, a predictable design flow is needed. The result should be a system that guarantees that an application can perform its own tasks within strict timing deadlines, independent of other applications running on the system. This requires that the timing behavior of the hardware, the software, as well as their interaction can be predicted.

A heterogeneous multi-processor System-on-Chip (MP-SoC) is often mentioned as the hardware platform to be used in modern electronics systems. An MP-SoC offers good potential for computational efficiency (operations per Joule) for many applications. Networks-on-Chip (NoCs) are proposed as interconnect in these systems. A NoC offers scalability and guarantees on the timing behavior when communicating data between various processing and storage elements. Combining this with a predictable resource arbitration strategy for the processors and storage elements gives a predictable platform. To obtain a fully predictable system, also the timing behavior and resource usage of an application mapped to such an MP-SoC platform needs to be analyzable and predictable. The Synchronous Dataflow (SDF) model of computation fits well with the characteristics of streaming applications, it can capture many mapping decisions, and it allows design-time analysis of timing and resource usage. Therefore, this thesis aims to achieve predictable, streaming application behavior on NoC-based MP-SoC platforms for applications modeled as SDF graphs (SDFGs).

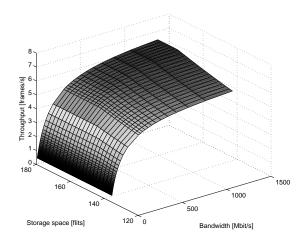

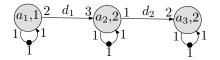

The most important timing requirement for streaming applications is usually related to the throughput that should be achieved. A major aspect influencing the achievable throughput, and in fact also the computational efficiency, is the storage space allocated to the data streams being processed in the system. In an SDFG model, the edges in the graph typically correspond to data streams. The storage allocation problem for an SDFG is the problem of assigning a fixed storage size to its edges. This size must be chosen such that the throughput requirement of the system is met, while minimizing the required storage space. The first major contribution of this thesis is an exact technique to explore the

i

throughput/storage-space trade-off space. Despite the theoretical complexity of the storage allocation problem, the technique performs well in practice. By considering the entire trade-off space, it is possible to cope with situations where the precise throughput constraint is not (yet) known or might dynamically change. In multi-processor mapping, for example, scheduling decisions can influence the achievable throughput. This introduces uncertainty on the relation between the throughput and the storage requirements of an SDFG in the early phases of the trajectory when these scheduling decisions are not yet made.

In any multi-processor mapping trajectory, an application must be bound to and scheduled onto the processors and storage elements in the MP-SoC. An important contribution of this thesis is such a technique to bind and schedule an SDFG onto an MP-SoC. Existing binding and scheduling techniques can only deal with single-rate execution dependencies between tasks. SDFGs can express multirate dependencies between tasks. Dependencies in an SDFG can be expressed in single-rate form, but then the problem size may increase exponentially making the binding and scheduling infeasible. The binding and scheduling technique presented in this thesis works directly on SDFGs, building on an efficient technique to calculate throughput of a bound and scheduled SDFG.

When the application tasks have been bound to and scheduled onto the platform components, it remains to schedule the communication onto the MP-SoC interconnect. This thesis presents three different scheduling strategies that schedule time-constrained communications on a NoC while minimizing resource usage by exploiting all scheduling freedom offered by NoCs. It is shown that these strategies outperform existing NoC scheduling techniques. Furthermore, a technique is presented to extract the timing constraints on the communication from a bound and scheduled SDFG, connecting the NoC scheduling strategies to the binding and scheduling strategy for SDFGs mentioned earlier.

Finally, the techniques presented in this thesis are embedded into a coherent design flow. The starting point is a streaming application that is modeled with an SDFG and a NoC-based MP-SoC that offers a predictable timing behavior. The objective of the flow is to minimize the resource usage while offering guarantees on the timing behavior, in practice the throughput, of the application when mapped to the system. A case study is performed that maps a set of multimedia applications (H.263 encoder/decoder and an MP3 decoder) onto a NoC-based MP-SoC. It shows that the design flow, SDFG mapping techniques, and SDFG analysis techniques presented in this thesis enable a mapping of a streaming application onto a NoC-based architecture that has a predictable timing behavior. This makes it the first complete design flow that maps a time-constrained SDFG to a NoC-based MP-SoC while providing throughput guarantees.

# Contents

| Abstract i |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                       |  |  |  |

|------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| 1          | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                            | roduction         Trends in Embedded Systems: A Consumers Perspective         Trends in Embedded Systems: A Designers Perspective         Problem Statement         A Predictable Design Flow         Contributions         Thesis Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>1</b><br>3<br>7<br>10<br>14<br>14                                  |  |  |  |

| <b>2</b>   | Stre                                                                      | eaming Multimedia Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                    |  |  |  |

| -          | 2.1                                                                       | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                    |  |  |  |

|            | 2.2                                                                       | Application Domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $17^{-1}$                                                             |  |  |  |

|            | 2.3                                                                       | Application Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                                    |  |  |  |

|            | 2.4                                                                       | Analyzing Actor Resource Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                                    |  |  |  |

|            | 2.5                                                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25                                                                    |  |  |  |

| 3          | Network-on-Chip-based Multi-Processor Platform                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                       |  |  |  |

| 3          | Net                                                                       | work-on-Chip-based Multi-Processor Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>27</b>                                                             |  |  |  |

| 3          | <b>Net</b><br>3.1                                                         | work-on-Chip-based Multi-Processor Platform Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>27</b><br>27                                                       |  |  |  |

| 3          |                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                       |  |  |  |

| 3          | 3.1                                                                       | Overview .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                                                                    |  |  |  |

| 3          | $3.1 \\ 3.2$                                                              | Overview   .     Multi-Processor Platform Template   .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27<br>27                                                              |  |  |  |

| 3          | 3.1<br>3.2<br>3.3                                                         | Overview       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .< | 27<br>27<br>29                                                        |  |  |  |

| 3          | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27<br>27<br>29<br>32                                                  |  |  |  |

|            | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27<br>27<br>29<br>32<br>34                                            |  |  |  |

|            | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>Dat                                    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27<br>27<br>29<br>32<br>34<br><b>35</b>                               |  |  |  |

|            | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br><b>Dat</b><br>4.1                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27<br>27<br>29<br>32<br>34<br><b>35</b><br>35                         |  |  |  |

|            | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br><b>Dat</b><br>4.1<br>4.2               | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27<br>27<br>29<br>32<br>34<br><b>35</b><br>35<br>35                   |  |  |  |

|            | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br><b>Dat</b><br>4.1<br>4.2<br>4.3        | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27<br>27<br>29<br>32<br>34<br><b>35</b><br>35<br>35<br>37             |  |  |  |

|            | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br><b>Dat</b><br>4.1<br>4.2<br>4.3<br>4.4 | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27<br>27<br>29<br>32<br>34<br><b>35</b><br>35<br>35<br>35<br>37<br>40 |  |  |  |

iii

|          | 4.8                        | Summary 52                                                                       |  |

|----------|----------------------------|----------------------------------------------------------------------------------|--|

| <b>5</b> | 5 Modeling Memory Mappings |                                                                                  |  |

|          | 5.1                        | Overview                                                                         |  |

|          | 5.2                        | Related Work                                                                     |  |

|          | 5.3                        | SDF model for Memory Accesses                                                    |  |

|          | 5.4                        | Memory Allocation                                                                |  |

|          | 5.5                        | Experimental Evaluation                                                          |  |

|          | 5.6                        | Summary                                                                          |  |

| C        | ъ                          |                                                                                  |  |

| 6        |                            | ource Allocation 67                                                              |  |

|          | 6.1                        | Overview                                                                         |  |

|          | 6.2                        | Related Work                                                                     |  |

|          | 6.3                        | Platform Graph                                                                   |  |

|          | 6.4                        | Resource-Aware Application Graph                                                 |  |

|          | 6.5                        | Resource Allocation Problem                                                      |  |

|          | 6.6                        | Throughput Analysis                                                              |  |

|          | 6.7                        | Resource Allocation Strategy 80                                                  |  |

|          | 6.8                        | Experimental Evaluation                                                          |  |

|          | 6.9                        | Summary                                                                          |  |

| 7        | $\mathbf{Thr}$             | oughput-Buffering Trade-Off Exploration 89                                       |  |

|          | 7.1                        | Overview                                                                         |  |

|          | 7.2                        | Related Work                                                                     |  |

|          | 7.3                        | Storage Requirements                                                             |  |

|          | 7.4                        | Storage Dependencies                                                             |  |

|          | 7.5                        | Design-Space Exploration                                                         |  |

|          | 7.6                        | Experimental Evaluation                                                          |  |

|          | 7.7                        | Approximation of Buffer Sizes                                                    |  |

|          | 7.8                        | Buffer Requirements for Binding-aware SDFGs                                      |  |

|          | 7.9                        | Summary                                                                          |  |

|          | 1.0                        |                                                                                  |  |

| 8        |                            | work-on-Chip Routing and Scheduling 113                                          |  |

|          | 8.1                        | Overview                                                                         |  |

|          | 8.2                        | Related Work                                                                     |  |

|          | 8.3                        | Communication Modeling 115                                                       |  |

|          | 8.4                        | Interconnect Graph                                                               |  |

|          | 8.5                        | Time-Constrained Scheduling Problem                                              |  |

|          | 8.6                        | Scheduling Strategies                                                            |  |

|          | 8.7                        | Benchmark                                                                        |  |

|          | 8.8                        | Experimental Evaluation                                                          |  |

|          | 8.9                        | Extracting Communication Scenarios from SDFGs $\ \ldots \ \ldots \ \ldots \ 136$ |  |

|          | 8.10                       | Summary                                                                          |  |

iv

| 9 Design Flow 143                                                                                                                                        |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 9.1 Overview                                                                                                                                             |  |  |  |  |  |

| 9.2 Related Work                                                                                                                                         |  |  |  |  |  |

| 9.3 Starting Point                                                                                                                                       |  |  |  |  |  |

| 9.4 MP-SoC Configuration                                                                                                                                 |  |  |  |  |  |

| 9.5 Memory Dimensioning $\ldots \ldots 151$                                 |  |  |  |  |  |

| 9.6 Constraint Refinement $\dots \dots \dots$            |  |  |  |  |  |

| 9.7 Tile Binding and Scheduling                                                                                                                          |  |  |  |  |  |

| 9.8 NoC Routing and Scheduling                                                                                                                           |  |  |  |  |  |

| 9.9 Implementation $\ldots \ldots 162$          |  |  |  |  |  |

| 9.10 Summary                                                                                                                                             |  |  |  |  |  |

| 10 Case Study 165                                                                                                                                        |  |  |  |  |  |

| 10.1 Overview                                                                                                                                            |  |  |  |  |  |

| 10.2 Applications $\ldots \ldots \ldots$ |  |  |  |  |  |

| 10.3 Hardware Architecture                                                                                                                               |  |  |  |  |  |

| 10.4 Mapping                                                                                                                                             |  |  |  |  |  |

| 10.5 Discussion on the Design Flow                                                                                                                       |  |  |  |  |  |

| 10.6 Summary                                                                                                                                             |  |  |  |  |  |

| 11 Conclusions and Future Work 18                                                                                                                        |  |  |  |  |  |

| 11.1 Conclusions                                                                                                                                         |  |  |  |  |  |

| 11.2 Open Problems and Future Research                                                                                                                   |  |  |  |  |  |

|                                                                                                                                                          |  |  |  |  |  |

| Bibliography 187                                                                                                                                         |  |  |  |  |  |

| Glossary 201                                                                                                                                             |  |  |  |  |  |

| Samenvatting 20                                                                                                                                          |  |  |  |  |  |

| Acknowledgments 22                                                                                                                                       |  |  |  |  |  |

| Curriculum Vitae 2                                                                                                                                       |  |  |  |  |  |

| List of Publications 2                                                                                                                                   |  |  |  |  |  |

v

vi

## Chapter 1

## Introduction

## 1.1 Trends in Embedded Systems: A Consumers Perspective

The number of consumer electronics devices sold worldwide is growing rapidly. A total of 2.1 billion consumer electronics devices with a total value of \$1.3 trillion were sold worldwide in 2006. It is expected that by 2010 this has grown to over 3 billion devices with a total value of around \$1.6 trillion [68]. Most of these devices contain one or more processors that are used to realize the functionality of the device. This type of devices are called **embedded systems**. Embedded systems range from portable devices such as digital cameras and MP3-players, to systems like a television or the systems controlling the flight of an airplane. These systems are everywhere around us in our daily live. Most of them are becoming intelligent micro-systems that interact with each other, and with people, through (wireless) sensors and actuators. Embedded systems form the basis of the so-called post-PC era [88], in which information processing is more and more moving away from just PCs to embedded systems. This trend is also signaled by ubiquitous computing [149], pervasive computing [57] and ambient intelligence [1]. These three visions describe all a world in which people are surrounded by networked embedded systems that are sensitive to their environment and that adapt to this environment. Their objective is to make information available *anytime*, *anywhere*. Embedded systems provide the necessary technology to realize these visions [16]. Realization of these visions implies that the number of embedded systems surrounding us in our daily lives will increase tremendously.

An important subclass of embedded systems are **embedded multimedia systems**. These systems combine multiple forms of information content and information processing (e.g. audio, video, animations, graphics) to inform or entertain the user. Examples of such systems are mobile phones, game consoles, smart cameras and set-top boxes. Many of the applications that perform the in-

Figure 1.1: Embedded multimedia systems: PlayStation 3 and iPhone.

formation processing in these systems process audio, video and animation. These types of data are inherently streaming. So, many embedded multimedia systems contain **streaming applications** [142]. These applications typically perform a regular sequence of transformations on a large (or virtually infinite) sequence of data items.

The functionality integrated into new embedded multimedia systems is ever increasing. The Sony PlayStation has, for example, transformed itself from a simple game console to a complete entertainment center. It not only allows users to play games, it can also be used to watch movies, listen to music and to browse the Internet or chat online with other PlayStation 3 users. Another example of a true multimedia platform is the Apple iPhone. It includes many different applications next to the mobile-phone functionality. It has, for example, a wide-screen LCD display that allows users to watch movies and browse through their collection of photos that are taken with the build-in camera. The phone contains also an MP3-player which allows users to listen for up-to 16 hours to their favorite music. While traveling, users can also use the phone to browse the Internet, send emails or use online navigation software such as Google-maps. It is expected that even more functions will be integrated into future embedded multimedia systems. This trend was already signaled by Vaandrager in 1998 who stated that "for many products in the area of consumer electronics the amount of code is doubling every two years" [145].

Current embedded multimedia systems have a robust behavior. Consider for example a modern high-end television system. Such a system splits the incoming video stream from its accompanying audio stream. Many different picture enhancement algorithms are executed on the video stream to improve its quality when displayed on the screen. Despite the complex processing going on inside the television, the video and audio stream are output in sync on the screen and the speakers. Consumers expect that future embedded multimedia systems provide the same robust behavior as current systems have despite the fact that more and more media processing is performed in software [26].

In summary, the following trends in embedded (multimedia) systems are observed from the perspective of consumers.

- The number of embedded systems surrounding people in their daily lives is growing rapidly, and these systems are becoming connected more and more often.

- Increasingly more functionality is integrated into a single multimedia system.

- Users expect the same seamless behavior of all functions offered by novel multimedia systems as offered by existing systems.

## 1.2 Trends in Embedded Systems: A Designers Perspective

The previous section outlines the most important trends in the field of embedded systems from the perspective of consumers. It shows that embedded systems have to handle an increasing number of applications that are concurrently executed on the system. At the same time, guarantees must be provided on the behavior of each application running on the system. This section considers the same systems, but it looks at the trends visible in their design(-process).

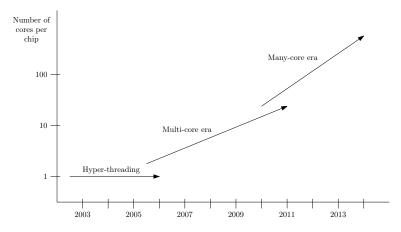

The omnipresence of embedded systems in people's lives is leading to a tremendous increase in the amount of data that is being used. Today, people have gigabytes of photos, music and video on their systems. That data must be processed in real-time to be made useful. Embedded systems must provide the required computational power to do this. At the same time, their energy consumption should be kept at a minimum as many of these devices are battery powered (e.g., mobile-phone, MP3-player, digital-camera). To fulfill these requirements, the use of **multi-processor systems-on-chip** (MP-SoCs) is becoming increasingly popular [15, 73]. For example, Intel has shifted from increasing the clock frequency of every processor generation to a strategy in which multiple cores are integrated on a single chip. This paradigm shift is outlined in their platform 2015 vision [25]. It describes the expected evolution of Intel processor architectures from single core systems, via multi-core systems toward many-core systems (see Figure 1.2). The Cell architecture [74] that is used in the PlayStation 3 is another example

Figure 1.2: Current and expected eras for Intel processor architectures [25].

that shows the increasing popularity of MP-SoCs. It combines a PowerPC core with 8 synergetic processors that are used for data-intensive processing. A third example is the Nexperia digital video platform [36] from NXP. It supports digital television, home gateway and networking, and set-top box applications. An advanced member of the Nexperia family is the PNX8550 that combines two Tri-Media processors, a MIPS processor and several hardware accelerators in a single chip.

An important design question that arises when developing an MP-SoC is whether a homogeneous or heterogeneous solution should be used. Amdahl observed that the less parallel portion of an application can limit the performance on a parallel system [6]. This observation is an important reason for using heterogeneous multi-processor systems. Different types of cores can be used in such a system to reduce the time needed to run the less parallel code. For example, consider an application in which 10% of the execution time is spent in code that cannot be executed in parallel on a 25-processor system. Suppose that in order to run this sequential code twice as fast, a processor would be needed that requires five times as much area as the cores used in the 25-processor system. A heterogenous 21-processor system with 20 cores similar to the cores used in the 25-processors and one core with the improved performance, would require the same area as the homogeneous 25-processor system. To compare the performance of both systems, the speed-up of the application on both systems can be computed using Amdahl's law [61]. This law computes the maximum expected improvement, i.e., reduction in run-time, to an overall system when only part of the system is improved. The speed-up of the application when executed on a homogeneous 25-processor system and a heterogenous 21-processor system relative to a sequential implementation of the application are:

$$Speedup_{homogeneous} = \frac{1}{0.1 + 0.9/25} = 7.4x$$

$$Speedup_{heterogeneous} = \frac{1}{0.1/2 + 0.9/20} = 10.5x$$

This example shows that using a **heterogeneous system** with some potentially large processors can be advantageous for the achieved speedup of the whole application. In addition, heterogeneous systems can show significant advantages in energy consumption as compared to homogeneous systems as the instruction set of the various processors can be optimized for their specific tasks.

The processing and storage elements that make up an MP-SoC must be interconnected. Traditionally, this has been done using on-chip buses or crossbar switches. These approaches do not scale very well when more processors are integrated in a system. To address these issues, **Networks-on-Chip** (NoCs) have been introduced [19, 32]. NoCs provide a scalable interconnect that can be shared between the processors and memories that are connected to it. Furthermore, it can provide guarantees on the time needed to send data through the NoC [93, 122]. This property makes NoCs suitable for use in MP-SoCs with a predictable timing behavior which is key for building reliable embedded multimedia systems.

The growing complexity of embedded multimedia systems leads to a large increase in their development effort. At the same time, the market dynamics for these systems push for shorter and shorter development times. It will soon be obligatory to keep to a strict design time budget that will be as small as six months to go from initial specification to a final and correct implementation [78]. Furthermore, the non-recurring engineering cost associated with the design and tooling of complex chips is growing rapidly. The International Technology Roadmap for Semiconductors (ITRS) predicts that while manufacturing complex Systems-on-Chip will be feasible, the production cost will grow rapidly as the costs of masks is raising drastically [69]. To address these issues, a platformbased design methodology is proposed in [39, 78]. The objective of this design methodology is to increase the re-use across different products that share certain functionality and the re-use between different product generations. The first form of re-use decreases the production cost as the same hardware can be used in more products. The second form of re-use lowers the development time as functionality implemented for a product does not have to be re-implemented for a successor product.

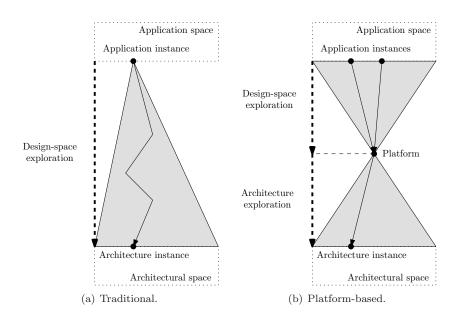

The traditional design methodology is a single monolithic flow that maps an application onto an architecture (see Figure 1.3(a)). It starts with a single application which is shown at the top of Figure 1.3(a). The bottom of the figure shows the set of architectures that could support this application. The design process (black arrow) selects the most attractive solution as defined by a cost function. Synthesis of this architecture is often an explicit objective of the de-

Figure 1.3: Design-space exploration strategies.

sign methodology [12, 38]. The platform-based design methodology [39, 78] no longer maps a single application to an architecture that is optimal for this single application. Instead, it maps an application onto a hardware/software platform that can also be used for different applications from the same application space (see Figure 1.3(b)). This platform consists of a set of interconnected hardware components (e.g., processors, memories, etc.), potentially software components with, for example, operating-system type of functionality and an application program interface (API) that abstracts from the underlying hardware and software. This API allows replacing one platform instance from the architecture space with another platform instance without the need to re-implement the application on the platform. The platform-based design methodology stimulates the use of a common "platform" denominator between multiple applications from the same application space. As a result, future design flows that map an application to a platform will focus on compiling an application onto an existing platform [78].

The trends signaled above show that the context in which applications are executed is becoming more dynamic. In future systems, multiple applications are running concurrently on an MP-SoC, and the set of active applications may change over time. At the same time, users expect a reliable behavior [10] of each individual application independent of the context in which it is operating. Virtualization of the resources in a system has been proposed as a concept to tackle this problem. The idea behind **virtualization** is that an application is given the illusion that it is running on its own copy of the real hardware which however has only a fraction of the resources that are available in the real platform. For example, a processor which can do 100 million instructions per second could use a Time-Division Multiple-Access (TDMA) scheduler to present itself to an application A as a processor which can run 50 million instructions per second. This leaves room for another application B to use the remaining 50 million instructions per second without knowing that application A is also running on this processor. Virtualization has become popular in recent years in server and desktop computers [25, 61]. The concept is also employed in embedded systems. The Cell architecture [74] of IBM uses virtualization to avoid that programmers have to think about sharing processing resources and to guarantee the real-time response characteristics of applications. The Hijdra architecture [17] of NXP is another example of an embedded multi-processor system that uses virtualization. This architecture assumes that every hardware component has a scheduler that allows it to be shared between applications without them influencing each others timing behavior.

In summary, the following trends in the design of embedded systems are observed from a design perspective.

- Heterogeneous multi-processor systems are used to provide the required computational power for novel embedded multimedia systems.

- Networks-on-chip are used to provide a scalable interconnect with timing guarantees between the processors in the system.

- Platform-based design reduces production cost, design cost and design time of embedded systems.

- Virtualization of resources is used to guarantee a predictable behavior of applications in a dynamic environment.

## 1.3 Problem Statement

The trends outlined in the first two sections of this chapter show that the design complexity of future embedded multimedia systems is growing rapidly. Consumers expect that the number of applications integrated into these systems is increased as compared to existing systems. At the same time, they expect that this increased functionality does not affect the reliable behavior and quality of these systems, and that the price of these systems does not increase (too much). System-designers do not only have to meet these criteria, they also have to cope with a decreasing time-to-market and increasing design cost. To deal with these conflicting requirements, designers are starting to use multi-processor systemson-chip, virtualization and a platform-based design methodology. The challenge is to combine these elements into a design method that enables designers to build systems with a predictable timing behavior. In such a **predictable system**, applications are mapped to a platform while timing guarantees are provided for each application independent of the other applications executing simultaneously on the platform.

This thesis deals with the design of systems with a predictable timing behavior. Three components are needed to build these systems. First, a platform must be used that offers a predictable timing behavior to individual applications independent of other applications running on the same platform. Second, a model should be used that allows timing analysis of the application and its mapping to the platform. Third, a design flow should be used that allocates sufficient resources for an application in the platform to meet its timing requirements. The remainder of this section discusses all three aspects in some more detail and it explains the choices made in this thesis.

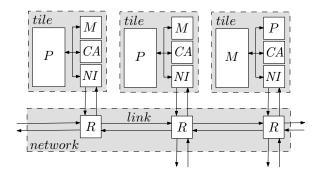

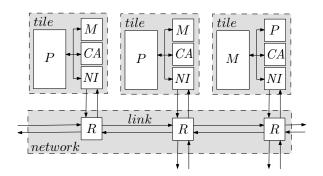

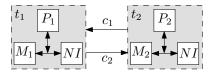

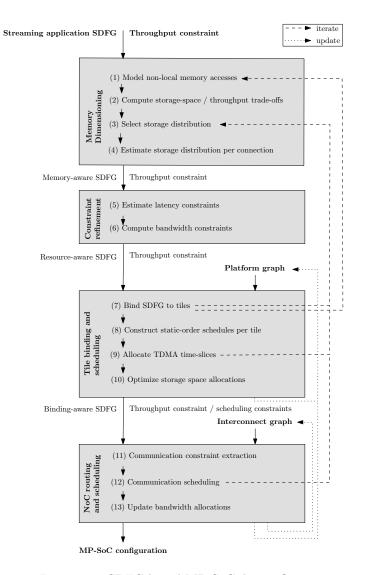

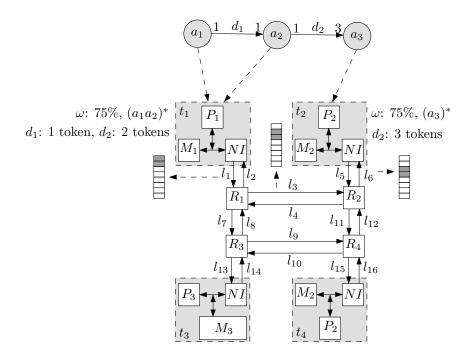

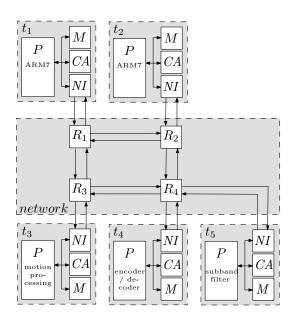

Multi-processor systems that use a NoC interconnect will be a dominant hardware platform in future embedded multimedia systems. The tile-based architecture presented in [30] enables the structured design of these NoC-based MP-SoCs. The template of this architecture allows any type of interconnect. Figure 1.4 shows the template instantiated with a NoC interconnect. Each tile contains a processor (P), a memory (M), a communication assist (CA) and a network interface (NI). The latter two resources are needed to decouple the computation from the communication and to connect the tile with the NoC. This NoC connects all tiles together via its routers (R) and links. To use this NoC-based MP-SoC in a predictable system, the platform should offer a resource sharing mechanism that allows multiple applications to use the platform resources simultaneously while guarantees can be provided on the amount of time an application has access to the resources and frequency of these accesses. A platform that offers these guarantees is called a **predictable platform**. The NoC-based MP-SoC shown in Figure 1.4 can be turned into a predictable platform through the use of virtualization on its resources. Due to the virtualization it is possible to consider a single application at a time when designing a system in which multiple applications are executed concurrently. This avoids that all combinations of applications have to be analyzed when verifying the timing constraints of an application that is mapped to the platform.

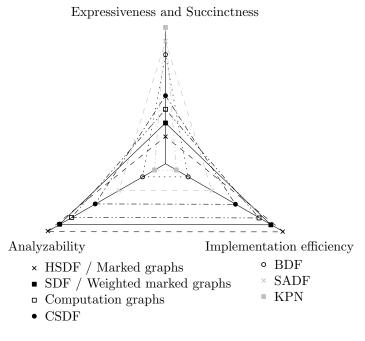

The design of a predictable system requires that the timing behavior of the application and its mapping to the platform can be analyzed. This can be done by modeling the application and mapping decisions in a **Model-of-Computation** (MoC) that allows timing analysis. A MoC captures, in an abstract manner, the relevant features of a computation [73]. Which features are relevant depends on the context in which a MoC is used. For the purpose of designing a predictable MP-SoC system, it is important that the MoC can express the concurrency that is present in an application. This concurrency should be exploited when mapping

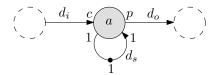

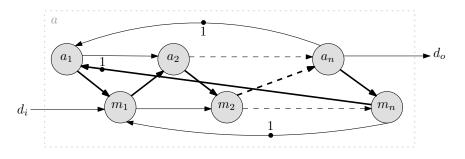

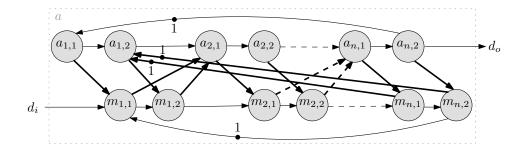

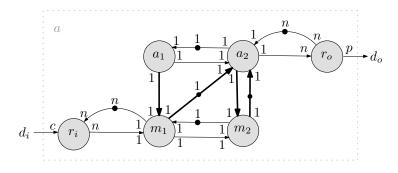

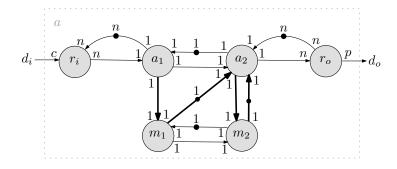

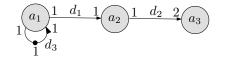

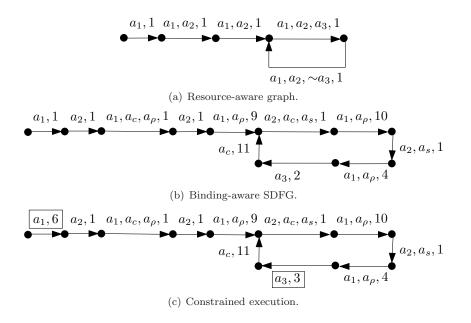

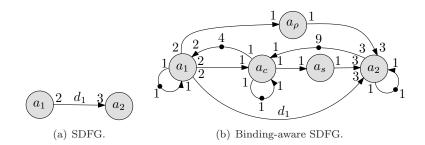

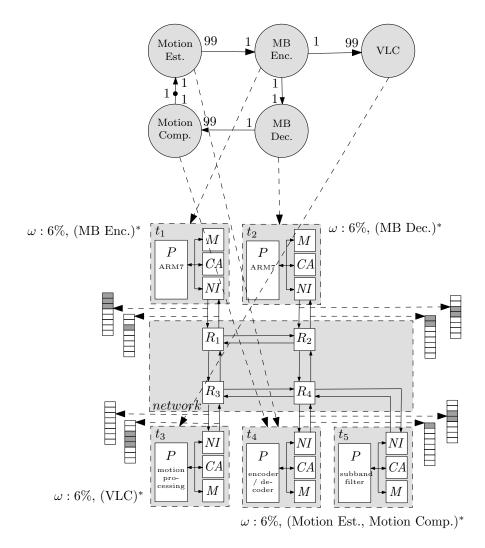

Figure 1.4: Predictable platform.

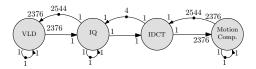

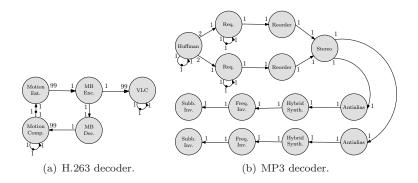

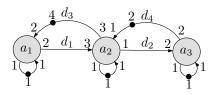

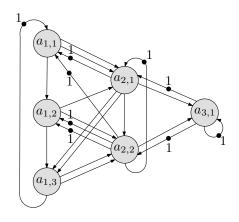

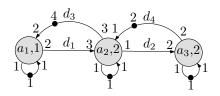

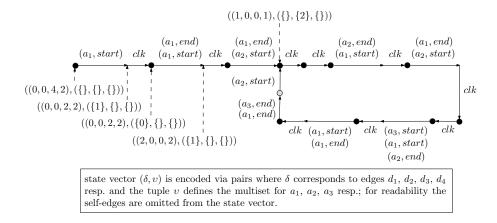

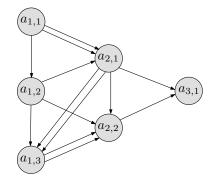

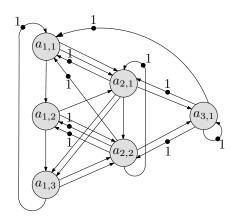

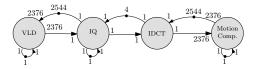

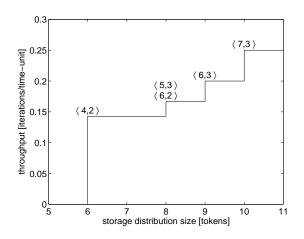

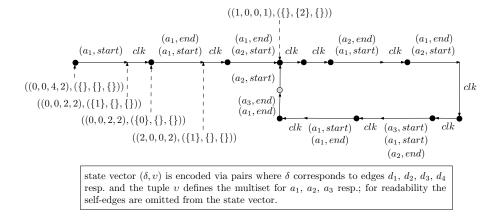

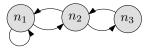

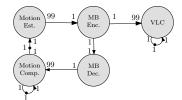

the application to the MP-SoC that is inherently concurrent. The MoC should also express the synchronization and communication between the concurrent tasks of an application. Concurrent tasks have to communicate with each other and they should be able to agree on the use of shared resources. Furthermore, the MoC must capture the timing behavior of the tasks and allow analysis of the timing behavior of the application. This makes it possible to verify whether the timing constraints imposed on the application are satisfied. Finally, the MoC should allow a natural description of the application in the model. Multimedia applications are typically streaming applications. The class of dataflow MoCs fits well with this behavior. A dataflow program is specified by a directed graph where the nodes (called **actors**) represent computations that communicate with each other by sending ordered streams of data-elements (called **tokens**) over their edges. The execution of an actor is called a **firing**. When an actor fires, it consumes tokens from its input edges, performs a computation on these tokens and outputs the result as tokens on its output edges. In this thesis, the **Synchronous Dataflow** (SDF) MoC is used to model streaming applications. Actors in an SDF graph (SDFG) consume and produce a fixed amount of tokens on each firing. This makes it possible to analyze the throughput [46] and latency [47, 128] of these graphs. An example of an SDFG modeling an H.263 decoder is shown in Figure 1.5. Every of the four actors performs part of the frame decoding. The frame decoding starts in the actor VLD and a complete frame is decoded when the data is processed by actor Motion Comp. (motion compensation). Data that must be preserved between subsequent firings of an actor is modeled with an initial token on the self-edges of the actors. The partially decoded data is communicated via the edges at the bottom (left-to-right). The edges at the top (right-to-left) model the storage-space constraints on the bottom edges. This shows another important property of SDFGs. They allow modeling of many mapping decisions in the graph [13]. This enables analysis of the timing behavior of the application under these design decisions.

Figure 1.5: SDFG of an H.263 decoder.

When building a predictable system, a predictable platform should be used. Furthermore, a MoC should be used which allows analysis of the timing behavior of an application under certain mapping decisions. The third aspect that should be considered when designing a predictable system is the design flow that maps an application to a platform. This design flow should reserve sufficient resources in the platform such that the application can meet its timing-constraints when executed on the platform. A design flow that can determine this mapping is called a **predictable design flow**.

In this work, it is assumed that a platform with a predictable timing behavior is available. It is also assumed that applications are modeled as SDFGs. This allows timing analysis of an application and its mapping to the platform. The third element, a predictable design flow, is studied in this thesis. The next section sketches the steps needed in a predictable design flow. It also introduces the most important problems that must be solved in developing such a flow.

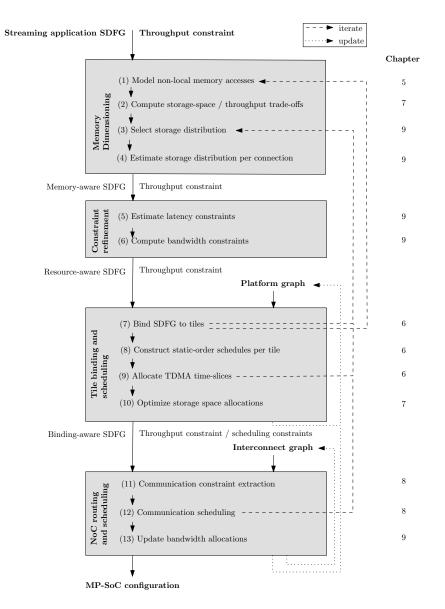

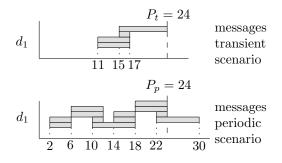

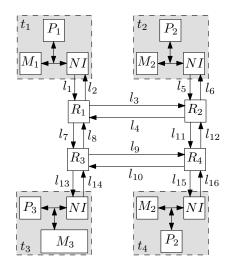

### 1.4 A Predictable Design Flow

This thesis presents techniques to map a time-constrained streaming application to a NoC-based MP-SoC. The objective is to minimize the resource usage (processing, memory, communication bandwidth) while offering guarantees on the throughput of the application when mapped to the system. A design flow that provides this guarantee is shown in Figure 1.6. The design flow consists of thirteen steps which are divided over four phases. This section introduces the various steps in the flow. The details of these steps can be found in the chapters mentioned in Figure 1.6. The motivation for the ordering of the steps in the flow can be found in Chapter 9.

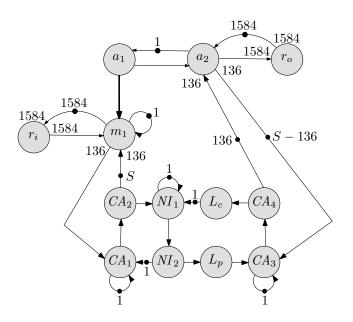

The design flow assumes that the application that it has to map to the NoCbased MP-SoC is modeled with a (streaming) application SDFG with accompanying throughput constraint. The application SDFG specifies for every actor the required memory space and execution time for all processors on which this actor can be executed. It also gives the size of the tokens communicated over the edges. The NoC-based MP-SoC is described with a platform graph and an interconnect graph. The **platform graph** describes all resources in the SoC except that it abstracts from the NoC interconnect. The NoC resources are captured in

Figure 1.6: SDFG-based MP-SoC design flow.

the **interconnect graph**. The result of the design flow is an **MP-SoC configuration** which specifies a binding of the actors to the processors and memories, a schedule for the actors on the processors and a schedule for the token communication over the NoC.

Tokens that are communicated over the edges of an application SDFG must be stored in memory. The allocation of storage space for these tokens is dealt with in the **memory dimensioning** phase. Some tokens might be too large to fit into the memory that is available inside the tiles executing the actors that process the data in these tokens. Such tokens should be placed in some remote tile which has sufficient memory space. The actors that use these tokens must then access the tokens over the NoC. These accesses to the NoC must be modeled in the SDFG to allow timing analysis of this design decision. The first step of the design flow identifies the tokens which should be stored in a remote tile. It also transforms the streaming application SDFG to model the design decision that these tokens are stored in this remote tile.

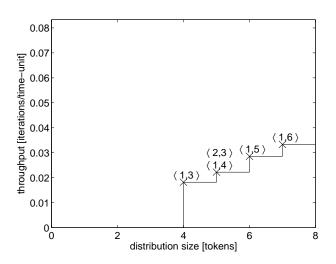

The streaming application has a throughput constraint that must be satisfied by the MP-SoC configuration. A major aspect influencing the achieved throughput is the storage space allocated to the edges of the graph. Allocating space for more than one token to an edge might increase throughput because it may increase pipelining opportunities. The size of the storage space must be chosen such that the throughput requirement is met, while minimizing the required storage space. As the exact throughput constraint for parts of the system at various stages of the design is often unknown, a trade-off must be made between the realizable throughput and the storage requirements for an SDFG. The second step of the flow computes the throughput-storage space trade-off space. It finds all distributions of storage space that achieve the maximal throughput under a given total storage size constraint. One of these storage distributions is selected in the third step of the flow to limit the storage space of the edges in the application SDFG. The source and destination actor of an edge might in the end be bound to different tiles. In that case, the storage space allocated to an edge has to be split over both tiles. Step 4 estimates the storage space that should be allocated in both tiles to meet the throughput constraint. The SDFG that results from the first phase of the design flow is called a **memory-aware SDFG**. It models access to tokens stored in a remote memory and it constrains the storage space of the edges in the graph.

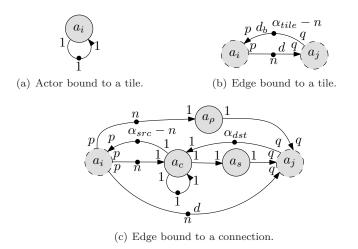

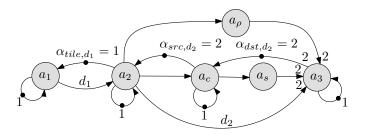

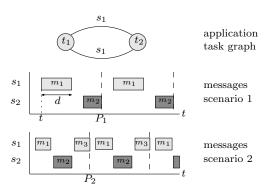

In the SDF MoC, it is assumed that edges have an infinite bandwidth and no latency. In other words, communication of tokens over an edge takes no time. Edges whose source and destination actors are bound to different tiles will be bound to a connection in the NoC. This connection has a latency and finite bandwidth. The **constraint refinement** phase of the design flow estimates the maximal latency (step 5) and minimal bandwidth (step 6) needed for edges when bound to a connection such that the throughput constraint is met. The resulting SDFG is called a **resource-aware SDFG**.

The constraints computed in steps 3 through 6 are used to steer the resource

#### 1. INTRODUCTION

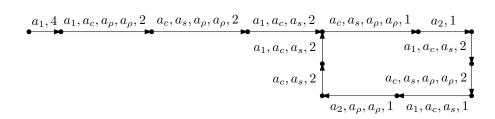

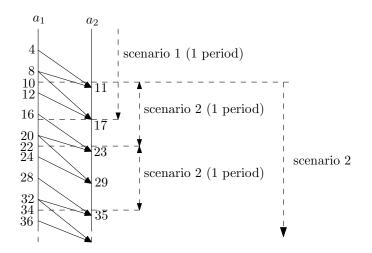

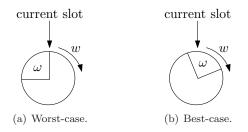

allocation that takes place in the third phase of the flow. This **tile binding and scheduling** phase binds actors and edges from the resource-aware SDFG to the resources in the platform graph (step 7). When a resource is shared between different actors or applications, a schedule should be constructed that orders the accesses to the resource. The accesses from the actors in the resource-aware SDFG to a resource are ordered using a static-order schedule. This schedule is constructed in step 8 of the flow. Step 9 allocates TDMA time slices on all resources that are used by the resource-aware SDFG. These TDMA time slices provide virtualization of the resources to the application.

The storage space allocated to the edges of the resource-aware SDFG could be too large when the mapping decisions made in step 7 through 9 are considered. Step 10 computes the throughput-storage space trade-off space of the resourceaware SDFG considering the binding and scheduling decisions taken so far. The storage space allocations of the edges are then updated based on the smallest storage space allocation from this trade-off space that satisfies the throughput constraint.

The third phase of the design flow, binds and schedules the actors to the resources of the platform. This phase does not consider the scheduling of the communication on the NoC. This problem is considered in the **NoC routing and scheduling** phase of the design flow. The actor bindings and schedules impose timing-constraints on the communication that must be met when constructing a communication schedule. These timing constraints are extracted from the binding-aware SDFG in step 11. Next, the communication is scheduled onto the NoC. The objective of the NoC scheduling is to minimize the resource usage while satisfying all timing constraints. Based on the actual bandwidth usage of the communication schedule, the resource availability in the platform and interconnect graph can be updated. This is done in step 13 of the design flow. The updated graphs can then be used to map another application on the same platform while considering the resources used by the already mapped application(s).

The mapping of the streaming application to the NoC-based MP-SoC may fail at various steps of the design flow. This may occur due to lack of resources (step 7) or infeasible timing constraints (step 9 and 12). In those situations, the design flow iterates back to the first or third step of the flow and design decisions made in those steps are revised. When going back to step 1, more or different tokens should be placed in a memory that is accessed over the NoC. Reverting back to step 3 implies that the storage space allocated to the edges is too constrained for meeting the throughput constraint. So, a different storage distribution should be chosen.

The design process ends as soon as a mapping of the application to the NoCbased MP-SoC is found that satisfies the throughput constraint or till all storage distributions from the space found in step 2 are tried unsuccessfully. In the latter case, the design flow is not able to find an MP-SoC configuration that satisfies the throughput constraint. More resources should be added to the platform or the application and its constraint should be modified in order to find an MP-SoC configuration that meets the throughput constraint.

### 1.5 Contributions

This thesis makes several contributions to develop a predictable design flow as sketched in the previous section.

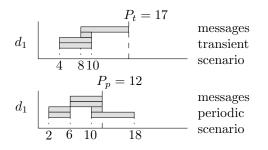

- An SDF model is presented that allows reasoning about the timing behavior of an actor which uses data stored in a memory that is accessed over an interconnect (Chapter 5). An earlier version of this work was published in [135, 136].

- A cost-function driven heuristic algorithm is proposed for binding and scheduling a throughput-constrained SDFG on the tiles of a multi-processor system (Chapter 6). This work was published in [132].

- An efficient technique is presented to calculate the throughput of a bound and scheduled SDFG (Chapter 6). This work was published in [132].

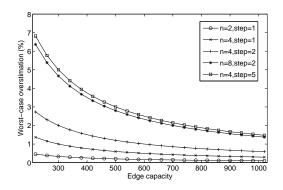

- An algorithm is presented to compute the trade-off space between storagespace allocation for the edges of an SDFG and the maximal throughput that can be realized under these storage constraints (Chapter 7). This work was published in [137].

- Several routing and scheduling algorithms for mapping time-constrained communication on a NoC are presented. These algorithms minimize resource usage by exploiting all scheduling freedom offered by NoCs while guaranteeing that the timing constraints are met (Chapter 8). This work was published in [134] and an extended version is published in a special issue of the Journal of Systems Architecture on the best papers of the Digital System Design conference [133].

- A design-flow is proposed that maps a throughput-constrained application modeled with an SDFG onto a NoC-based MP-SoC (Chapter 9).

- The SDF<sup>3</sup> tool-kit implements all techniques presented in this thesis, the predictable design-flow and existing SDFG analysis and visualization techniques, as well as a graph generator (Chapter 4). An earlier version of this work has been published in [138].

### 1.6 Thesis Overview

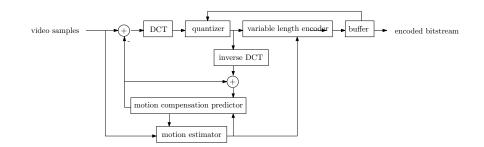

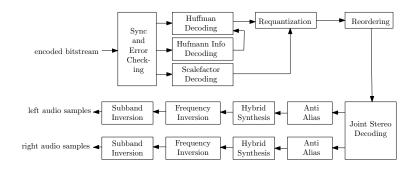

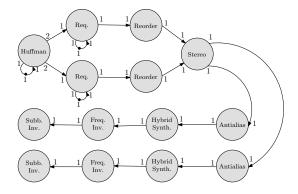

This thesis is organized as follows. The next chapter discusses the characteristics of modern streaming multimedia applications. It considers both the modeling of these applications as dataflow graphs as well as the estimation of their resource requirements. Chapter 3 presents the NoC-based MP-SoC platform template assumed in this thesis with its scheduling strategies. These scheduling strategies make sure that the platform can provide timing guarantees to individual applications when these applications reserve resources from the platform. The synchronous dataflow model is introduced in Chapter 4. This chapter discusses also existing techniques for analyzing the throughput of an SDFG and scheduling it on single and multi-processor systems. Chapter 5 presents an SDF model that allows reasoning about the timing behavior of an actor that uses data stored in a memory that is accessed over the NoC. A technique to bind and schedule an SDFG to the resources of an MP-SoC is presented in Chapter 6. The minimal storage-space for the edges of an SDFG that must be allocated by this binding and scheduling technique can be computed using the algorithm presented in Chapter 7. This algorithm can compute the complete trade-off space between the storagespace and throughput of an SDFG. The resource allocation technique presented in Chapter 6 does not construct a schedule for the communication on the NoC. Several scheduling techniques for this problem are presented in Chapter 8. All techniques presented in this thesis are embedded into a coherent and complete design flow in Chapter 9. A case study is performed in Chapter 10 that maps a set of multimedia applications (H.263 encoder/decoder and an MP3 decoder) onto a NoC-based MP-SoC. Finally, Chapter 11 concludes this thesis and gives recommendations for future work.

1.6. THESIS OVERVIEW

## Chapter 2

# **Streaming Multimedia Applications**

## 2.1 Overview

This chapter gives an overview of the main characteristics of streaming multimedia applications. Section 2.2 introduces the application domain and its most widely used applications. The properties that should be captured when modeling these applications are discussed in Section 2.3. To perform timing analysis and resource allocation, properties like the execution time and required memory space need to be extracted from an application. Section 2.4 discusses techniques to extract these requirements from the source code of applications.

## 2.2 Application Domain

Multimedia applications constitute a huge application space for embedded systems. They underlie many common entertainment devices, for example, cell phones, digital set-top boxes and digital cameras. Most of these devices deal with the processing of audio and video streams. This processing is done by applications that perform functions like object recognition, object detection and image enhancement on the streams. Typically, these streams are compressed before they are transmitted from the place where they are recorded (**sender**) to the place where the are played-back (**receiver**). Applications that compress and decompress audio and video streams are therefore among the most dominant streaming multimedia applications [152].